# **Chapter 17 SPDIF transmitter**

# 17.1 Overview

The SPDIF transmitter is a self-clocking, serial, unidirectional interface for the interconnection of digital audio equipment for consumer and professional applications, using linear PCM coded audio samples.

It provides the basic structure of the interface. Separate documents define items specific to particular applications.

When used in a professional application, the interface is primarily intended to carry monophonic or stereophonic programmes, at a 48 kHz sampling frequency and with a resolution of up to 24bits per sample; it may alternatively be used to carry signals sampled at 32 kHz or 44.1 kHz.

When used in a consumer application, the interface is primarily intended to carry stereophonic programmes, with a resolution of up to 20 bits per sample, an extension to 24 bits per sample being possible.

When used for other purposes, the interface is primarily intended to carry audio data coded other than as linear PCM coded audio samples. Provision is also made to allow the interface to carry data related to computer software or signals coded using non-linear PCM. The format specification for these applications is not part of this standard.

In all cases, the clock references and auxiliary information are transmitted along with the programme.

- Supports one internal 32-bit wide and 32-location deep sample data buffer

- Supports two 16-bit audio data store together in one 32-bit wide location

- Supports AHB bus interface

- Supports biphase format stereo audio data output

- Supports DMA handshake interface and configurable DMA water level

- Supports sample data buffer empty, block terminate and user data interrupt

- Supports combine interrupt output

- Supports 16 to 31 bit audio data left or right justified in 32-bit wide sample data buffer

- Support 16, 20, 24 bits audio data transfer in linear PCM mode

- Support non-linear PCM transfer

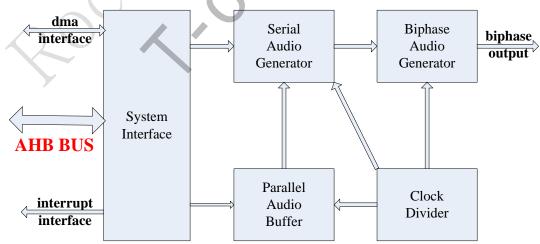

## 17.2 Block Diagram

Fig. 17-1 SPDIF transmitter Block Diagram

#### System Interface

The system interface implements the AHB slave operation. It contains not only control registers of transmitters and receiver inside but also interrupt and DMA handshake interface.

#### **Clock Divider**

The Clock Divider implements clock generation function. The input source clock to the module is MCLK, and by the divider of the module, the clock divider generates work clock for digital audio data transformation.

#### **Parallel Audio Buffer**

The Parallel Audio Buffer is the buffer to store transmitted audio data. The size of the FIFO is 32bits  $\times$  32.

#### **Serial Audio Converter**

The Serial Audio Converter reads parallel audio data from the Parallel Audio Buffer and converts it to serial audio data.

#### **Biphase Audio Generator**

The Biphase Audio Generator reads serial audio data from the Serial Audio Converter and generates biphase audio data based on IEC-60958 standard.

## **17.3 Function description**

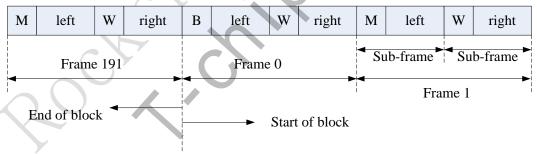

## 17.3.1 Frame Format

A frame is uniquely composed of two sub-frames. For linear coded audio applications, the rate of transmission of frames corresponds exactly to the source sampling frequency.

In the 2-channel operation mode, the samples taken from both channels are transmitted by time multiplexing in consecutive sub-frames. The first sub-frame(left channel in stereophonic operation and primary channel in monophonic operation) normally use preamble M. However, the preamble is changed to preamble B once every 192 frame to identify the start of the block structure used to organize the channel status information. The second sub-frame (right in stereophonic operation and secondary channel in monophonic operation) always use preamble W.

Fig. 17-2 SPDIF Frame Format

In the single channel operation mode in a professional application, the frame format is the same as in the 2-channel mode. Data is carried only in the first sub-frame and may be duplicated in the second sub-frame. If the second sub-frame is not carrying duplicate data, then time slot 28 (validity flag) shall be set to logical '1' (not valid).

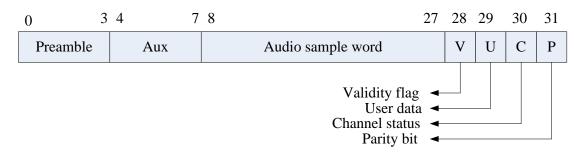

## 17.3.2 Sub-frame Format

Fig. 17-3 SPDIF Sub-frame Format

Each sub-frame is divided into 32 time slots, numbered from 0 to 31. Time slot 0 to 3 carries one of the three permitted preambles. Time slot 4 to 27 carry the audio sample word in linear 2's complement representation. The MSB is carried by time slot 27. When a 24-bit coding range is used, the LSB is in time slot 4. When a 20-bit coding range is used, time slot 8 to 27 carry the audio sample word with the LSB in time slot 8. Time slot 4 to 7 may be used for other application. Under these circumstances, the bits in the time slot 4 to 7 are designated auxiliary sample bits.

If the source provides fewer bits than the interface allows (either 24 or 20), the unused LSBs are set to a logical '0'. For a non-linear PCM audio application or a data application the main data field may carry any other information. Time slot 28 carries the validity flag associated with the main data field. Time slot 29 carries 1 bit of the user data associated with the audio channel transmitted in the same sub-frame. Time slot 30 carries one bit of the channel status words associated with the main data field channel transmitted in the same sub-frame. Time slot 31 carries a parity bit such that time slots 4 to 31 inclusive carries an even number of ones and an even number of zeros.

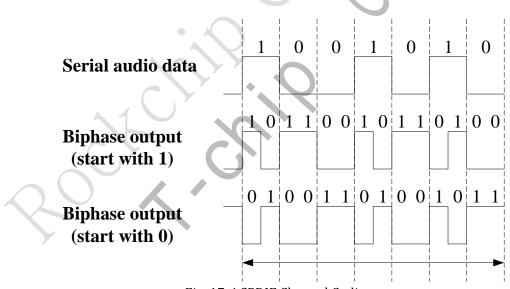

### 17.3.3 Channel Coding

Fig. 17-4 SPDIF Channel Coding

To minimize the direct current component on the transmission line, to facilitate clock recovery from the data stream and to make the interface insensitive to the polarity of connections, time slots 4 to 31 are encoded in biphase-mark.

Each bit to be transmitted is represented by a symbol comprising two consecutive binary states. The first state of a symbol is always different from the second state of the previous symbol. The second state of the symbol is identical to the first if the bit to be transmitted is logical '0'. However, it is different from the first if the bit is logical '1'.

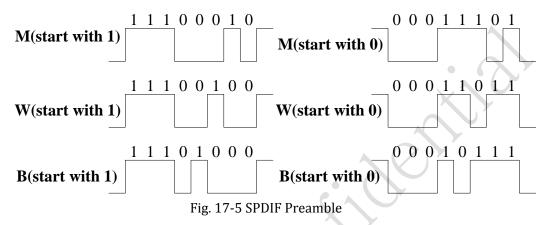

## 17.3.4 Preamble

Preambles are specific patterns providing synchronization and identification of the sub-frames and blocks.

To achieve synchronization within one sampling period and to make this process completely reliable, these patterns violate the biphase-mark code rules, thereby avoiding the possibility of data imitating the preambles.

A set of three preambles is used. These preambles are transmitted in the time allocated to four time slots (time slots 0 to 3) and are represented by eight successive states. The first state of the preamble is always different from the second state of the previous symbol.

Like biphase code, these preambles are dc free and provide clock recovery. They differ in at least two states from any valid biphase sequence.

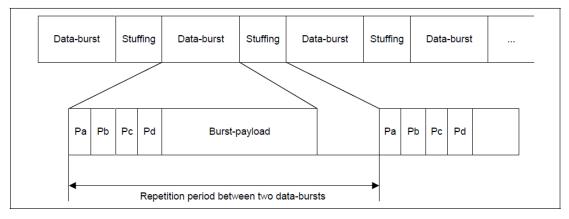

## 17.3.5 NON-LINEAR PCM ENCODED SOURCE(IEC 61937)

The non-linear PCM encoded audio bitstream is transferred using the basic 16-bit data area of the IEC 60958subframes, i.e. in time slots 12 to 27. Each IEC 60958 frame transfers 32-bit of the non-PCM data in consumer application mode.

If the SPDIF bitstream conveys linear PCM audio, the symbol frequency is 64 times the PCM sampling frequency (32 time slots per PCM sample times two channels). If a non-linear PCM encoded audio bitstream is conveyed by the interface, the symbol frequency is 64 times the sampling rate of the encoded audio within that bitstream. But in the case where a non-linear PCM encoded audio bitstream is conveyed by the interface containing audio with low sampling frequency, the symbol frequency is 128 times the sampling rate of the encoded audio within that bitstream.

Each data burst contains a burst-preamble consisting of four 16-bit words (Pa, Pb, Pc, Pd), followed by the burstpayload which contains data of an encoded audio frame.

The burst-preamble consists of four mandatory fields. Pa and Pb represent a synchronization word; Pc gives information about the type of data and some information/control for the receiver; Pd gives the length of the burstpayload, the number of bits or number of bytes according to data-type.

The four preamble words are contained in two sequential SPDIF frames. The frame beginning the data-burst contains preamble word Pa in subframe 0 and Pb in subframe 1. The next frame contains Pc in subframe 0 and Pd in subframe 1. When placed into a SPDIF subframe, the MSB of a 16-bit burst-preamble is placed into time slot 27 and the LSB is placed into time slot 12.

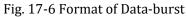

# 17.4 Register description

## **17.4.1 Register Summary**

| Name                    | Offset | Size | Reset<br>Value | Description                           |

|-------------------------|--------|------|----------------|---------------------------------------|

| SPDIF_CFGR              | 0x0000 | W    | 0×00000000     | Transfer Configuration<br>Register    |

| SPDIF_SDBLR             | 0x0004 | W    | 0×00000000     | Sample Date Buffer Level<br>Register  |

| SPDIF_DMACR             | 0x0008 | W    | 0x0000000      | DMA Control Register                  |

| SPDIF_INTCR             | 0x000c | W    | 0x0000000      | Interrupt Control Register            |

| SPDIF_INTSR             | 0x0010 | W    | 0x0000000      | Interrupt Status Register             |

| SPDIF_XFER              | 0x0018 | W    | 0x0000000      | Transfer Start Register               |

| SPDIF_SMPDR             | 0x0020 | W    | 0x0000000      | Sample Data Register                  |

| SPDIF_VLDFRn            | 0x0060 | W    | 0x00000000     | Validity Flag Register n              |

| SPDIF_USRDRn            | 0x0090 | W    | 0x00000000     | User Data Register n                  |

| SPDIF_CHNSRn            | 0x00c0 | W    | 0x0000000      | Channel Status Register n             |

| SPDIF_BURTSINFO         | 0x0100 | W    | 0x0000000      | Channel Burst Info Register           |

| SPDIF_REPETTION         | 0x0104 | W    | 0x00000000     | Channel Repetition Register           |

| SPDIF_BURTSINFO_<br>SHD | 0x0108 | W    | 0x00000000     | Shadow Channel Burst Info<br>Register |

| SPDIF_REPETTION_S<br>HD | 0x010c | W    | 0x00000000     | Shadow Channel Repetition<br>Register |

| SPDIF_USRDR_SHDn        | 0x0190 | W    | 0x0000000      | Shadow User Data Register n           |

Notes: <u>Size</u> : **B** - Byte (8 bits) access, **HW** - Half WORD (16 bits) access, **W** -WORD (32 bits) access

## 17.4.2 Detail Register Description

#### SPDIF\_CFGR

Address: Operational Base + offset (0x0000) Transfer Configuration Register

| Bit   | Attr | <b>Reset Value</b> | Description |

|-------|------|--------------------|-------------|

| 31:24 | RO   | 0x0                | reserved    |

| Bit   | Attr      | Reset Value | Description                                    |

|-------|-----------|-------------|------------------------------------------------|

|       |           |             | MCD                                            |

|       |           |             | mclk divider                                   |

| 22.10 |           | 000         | Fmclk/Fsdo                                     |

| 23:16 | RW        | 0x00        | This parameter can be caculated by             |

|       |           |             | Fmclk/(Fs*128).                                |

|       |           |             | Fs=the sample frequency be wanted              |

| 15:10 | RO        | 0x0         | reserved                                       |

|       |           |             | PRE_CHANGE                                     |

|       |           |             | Preamble Change                                |

|       |           |             | The bit only is valid when set to non-linear   |

| 9     | RW        | 0x0         | PCM mode;                                      |

|       |           |             | 0: the Preamble will change when block finish; |

|       |           |             | 1: the Preamble will change every 192 frames   |

|       |           |             | just like the linear PCM mode.                 |

|       |           |             | РСМТҮРЕ                                        |

|       |           | 0x0         | PCM type                                       |

| 8     | RW        |             | 0: linear PCM                                  |

|       |           |             | 1: non-linear PCM                              |

|       |           |             | CLR                                            |

| _     |           |             | mclk domain logic clear                        |

| 7     | WO        | 0x0         | Write 1 to clear mclk domain logic. Read       |

|       |           |             | return zero.                                   |

|       |           |             | CSE                                            |

|       |           |             | Channel status enable                          |

|       |           |             | 0: disable                                     |

| 6     | RW        | 0x0         | 1: enable                                      |

|       |           |             | The bit should be set to 1 when the channel    |

|       |           |             | conveys non-linear PCM                         |

|       |           |             | UDE                                            |

|       |           | 0×0         | User data enable                               |

| 5     | RW        |             | 0: disable                                     |

|       |           |             | 1: enable                                      |

|       | $\square$ |             | VFE                                            |

| くと    |           |             | Validity flag enable                           |

| 4     | RW        | 0x0         | 0: disable                                     |

| ×     |           |             | 1: enable                                      |

|       |           |             | ADJ                                            |

|       |           |             | audio data justified                           |

| 3     | RW        | 0×0         | 0: Right justified                             |

|       |           |             | 1: Left justified                              |

|       |           |             |                                                |

| Bit | Attr | Reset Value | Description                                    |

|-----|------|-------------|------------------------------------------------|

|     |      |             | HWT                                            |

|     |      |             | Halfword word transform enable                 |

| 2   | RW   | 0x0         | 0: disable                                     |

| 2   | K VV | 0.00        | 1: enable                                      |

|     |      |             | It is valid only when the valid data width is  |

|     |      |             | 16bit.                                         |

|     |      |             | VDW                                            |

|     |      | 0x0         | Valid data width                               |

|     |      |             | 00: 16bit                                      |

| 1:0 | RW   |             | 01: 20bit                                      |

| 1.0 | K VV |             | 10: 24bit                                      |

|     |      |             | 11: reserved                                   |

|     |      |             | The valid data width is 16bit only for $igcup$ |

|     |      |             | non-linear PCM                                 |

#### SPDIF\_SDBLR

Address: Operational Base + offset (0x0004) Sample Date Buffer Level Register

| Bit  | Attr | Reset Value | Description                                  |

|------|------|-------------|----------------------------------------------|

| 31:6 | RO   | 0x0         | reserved                                     |

|      |      | 0×00        | SDBLR                                        |

| 5.0  | RW   |             | Sample Date Buffer Level Register            |

| 5:0  | RVV  |             | Contains the number of valid data entries in |

|      |      |             | the sample data buffer.                      |

#### SPDIF\_DMACR

Address: Operational Base + offset (0x0008) DMA Control Register

| Bit  | Attr | Reset Value | Description                                       |

|------|------|-------------|---------------------------------------------------|

| 31:6 | RO   | 0x0         | reserved                                          |

|      |      | Y C         | TDE                                               |

| 5    | RW   | 0x0         | Transmit DMA Enable                               |

| 5    |      | UXU         | 0: Transmit DMA disabled                          |

|      |      |             | 1: Transmit DMA enabled                           |

|      |      | -           | TDL                                               |

|      |      |             | Transmit Data Level                               |

|      | RW   | 0×00        | This bit field controls the level at which a DMA  |

| 4:0  |      |             | request is made by the transmit logic. It is      |

| 4.0  |      |             | equal to the watermark level; that is, the        |

|      |      |             | dma_tx_req signal is generated when the           |

|      |      |             | number of valid data entries in the Sample        |

|      |      |             | Date Buffer is equal to or below this field value |

#### SPDIF\_INTCR

Address: Operational Base + offset (0x000c)

| Bit   | Attr      | Reset Value | Description                                       |

|-------|-----------|-------------|---------------------------------------------------|

| 31:18 | RO        | 0x0         | reserved                                          |

|       |           |             | UDTIC                                             |

| 17    | W1C       | 0x0         | Ueser Data Interrupt Clear                        |

|       |           |             | Write '1' to clear the user data interrupt.       |

|       |           |             | BTTIC                                             |

| 16    | W1C       | 0x0         | Block/Data burst transfer finish interrupt clea   |

|       |           |             | Write 1 to clear the interrupt.                   |

| 15:10 | RO        | 0x0         | reserved                                          |

|       |           |             | SDBT                                              |

| 0.F   | DW        | 0.400       | Sample Date Buffer Threshold                      |

| 9:5   | RW        | 0x00        | Sample Date Buffer Threshold for empty            |

|       |           |             | interrupt                                         |

|       |           |             | SDBEIE                                            |

| 1     | DW        | 0.40        | Sample Date Buffer empty interrupt enable         |

| 4     | RW        | 0x0         | 0: disable                                        |

|       |           |             | 1: enable                                         |

|       |           |             | BTTIE                                             |

|       |           |             | Block transfer/repetition period end interrupt    |

|       |           |             | enable                                            |

|       |           |             | When enabled, an interrupt will be asserted       |

| 3     | RW        | 0x0         | when the block transfer is finished if the        |

| 2     | RVV       | UXU         | channel conveys linear PCM or when the            |

|       |           |             | repetition period is reached if the channel       |

|       |           |             | conveys non-linear PCM.                           |

|       |           | •           | 0: disable                                        |

|       |           |             | 1: enable                                         |

|       |           |             | UDTIE                                             |

|       |           | C           | User Data Interrupt                               |

|       |           |             | 0: disable                                        |

| 2     | RW        | 0x0         | 1: enable                                         |

|       |           |             | If enabled, an interrupt will be asserted when    |

|       | $\bigcap$ |             | the content of the user data register is fed into |

| くと    |           |             | the corresponding shadow register                 |

| 1:0   | RO        | 0x0         | reserved                                          |

Interrupt Control Register

#### SPDIF\_INTSR

Address: Operational Base + offset (0x0010) Interrupt Status Register

| Bit  | Attr | Reset Value | Description                               |

|------|------|-------------|-------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                  |

|      |      | 0x0         | SDBEIS                                    |

| 1    |      |             | Sample Date Buffer empty interrupt status |

| 4    | RW   |             | 0: inactive                               |

|      |      |             | 1: active                                 |

| Bit | Attr  | Reset Value | Description                                |

|-----|-------|-------------|--------------------------------------------|

|     |       |             | BTTIS                                      |

| 3   | RW    | 0x0         | Block/Data burst transfer interrupt status |

| 5   | r, vv | UXU         | 0: inactive                                |

|     |       |             | 1: active                                  |

|     |       |             | UDTIS                                      |

|     |       |             | User Data Interrupt Status                 |

| 2   | RW    | 0x0         | 0: inactive                                |

|     |       |             | 1: active                                  |

|     |       |             |                                            |

| 1:0 | RO    | 0x0         | reserved                                   |

#### SPDIF\_XFER

Address: Operational Base + offset (0x0018) Transfer Start Register

| Bit  | Attr | Reset Value | Description             |

|------|------|-------------|-------------------------|

| 31:1 | RO   | 0x0         | reserved                |

|      |      |             | XFER                    |

| 0    | RW   | 0x0         | Transfer Start Register |

|      |      |             | Transfer Start Register |

#### SPDIF\_SMPDR

Address: Operational Base + offset (0x0020) Sample Data Register

| 2 |      | egister |                    |                      |

|---|------|---------|--------------------|----------------------|

|   | Bit  | Attr    | <b>Reset Value</b> | Description          |

|   |      |         | •                  | SMPDR                |

|   | 31:0 | RW      | 0x0000000          | Sample Data Register |

|   |      |         |                    | Sample Data Register |

#### SPDIF\_VLDFRn

Address: Operational Base + offset (0x0060) Validity Flag Register n

| Bit   | Attr         | Reset Value | Description                  |

|-------|--------------|-------------|------------------------------|

|       | $\mathbf{O}$ |             | VLDFR_SUB_1                  |

| 31:16 | RW           | 0x0000      | Validity Flag Subframe 1     |

|       |              | Ť           | Validity Flag Register 0     |

|       |              |             | VLDFR_SUB_0                  |

| 15:0  | RW           | 0x0000      | Validity Flag Subframe 0     |

|       |              |             | Validity Flag for Subframe 0 |

#### SPDIF\_USRDRn

Address: Operational Base + offset (0x0090)

User D<u>ata Register n</u>

| Bit Attr Reset Value Description |  |

|----------------------------------|--|

|----------------------------------|--|

| Bit   | Attr | Reset Value | Description                  |

|-------|------|-------------|------------------------------|

|       |      |             | USR_SUB_1                    |

| 31:16 | RW   | 0x0000      | User Data Subframe 1         |

|       |      |             | User Data Bit for Subframe 1 |

|       |      |             | USR_SUB_0                    |

| 15:0  | RW   | 0x0000      | User Data Subframe 0         |

|       |      |             | User Data Bit for Subframe 0 |

### SPDIF\_CHNSRn

Address: Operational Base + offset (0x00c0) Channel Status Register n

| Bit   | Attr | Reset Value | Description                       |

|-------|------|-------------|-----------------------------------|

|       |      |             | CHNSR_SUB_1                       |

| 31:16 | RW   | 0x0000      | Channel Status Subframe 1         |

|       |      |             | Channel Status Bit for Subframe 1 |

|       |      |             | CHNSR_SUB_0                       |

| 15:0  | RW   | 0x0000      | Channel Status Subframe 0         |

|       |      |             | Channel Status Bit for Subframe 0 |

#### SPDIF\_BURTSINFO

Address: Operational Base + offset (0x0100) Channel Burst Info Register

| Bit      | Attr | Reset Value                                                                                                          | Description                                                                                                              |

|----------|------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 31:16 RW |      | 0x0000                                                                                                               | PD<br>pd<br>Preamble Pd for non-linear pcm, indicating the                                                               |

|          |      | •                                                                                                                    | length of burst payload in unit of bytes or bits.                                                                        |

| 15:13    | RW   | 0x0<br>BSNUM<br>Bitstream Number<br>This field indicates the bitstream number.<br>Usually the birstream number is 0. |                                                                                                                          |

| 12:8     | RW   | 0×00                                                                                                                 | DATAINFO<br>Data-type-dependent info<br>This field gives the data-type-dependent info                                    |

| 7        | RW   | 0×0                                                                                                                  | ERRFLAG<br>Error Flag<br>0: indicates a valid burst-payload<br>1: indicates that the burst-payload may<br>contain errors |

| Bit | Attr | Reset Value | Description                                 |

|-----|------|-------------|---------------------------------------------|

|     |      |             | DATATYPE                                    |

|     |      |             | Data type                                   |

|     |      |             | 0000000: null data                          |

|     |      |             | 0000001: AC-3 data                          |

|     |      |             | 0000011: Pause data                         |

|     |      |             | 0000100: MPEG-1 layer 1 data                |

|     |      |             | 0000101: MPEG-1 layer 2 or 3 data or MPEG-2 |

|     |      |             | without extension                           |

|     |      |             | 0000110: MPEG-2 data with extension         |

|     |      |             | 0000111: MPEG-2 AAC                         |

|     |      |             | 0001000: MPEG-2, layer-1 low sampling       |

|     |      |             | frequency                                   |

|     |      |             | 0001001: MPEG-2, layer-2 low sampling       |

|     |      |             | frequency                                   |

|     |      |             | 0001010: MPEG-2, layer-3 low sampling       |

|     |      |             | frequency                                   |

|     |      |             | 0001011: DTS type I                         |

|     |      |             | 0001100: DTS type II                        |

|     |      |             | 0001101: DTS type III                       |

|     |      |             | 0001110: ATRAC                              |

| 6:0 | RW   | 0x00        | 0001111: ATRAC 2/3                          |

| 010 |      |             | 0010000: ATRAC-X                            |

|     |      |             | 0010001: DTS type IV                        |

|     |      |             | 0010010: WMA professional type I            |

|     |      |             | 0110010: WMA professional type II           |

|     |      | • ^         | 1010010: WMA professional type III          |

|     |      |             | 1110010: WMA professional type IV           |

|     |      | Y'          | 0010011: MPEG-2 AAC low sampling            |

|     |      |             | frequency                                   |

|     |      |             | 0110011: MPEG-2 AAC low sampling            |

|     | C    |             | frequency                                   |

|     |      |             | 1010011: MPEG-2 AAC low sampling            |

|     |      | 11          | frequency                                   |

|     |      |             | 1110011: MPEG-2 AAC low sampling            |

|     |      |             | frequency                                   |

|     |      |             | 0010100: MPEG-4 AAC                         |

|     |      |             | 0110100: MPEG-4 AAC                         |

|     |      |             | 1010100: MPEG-4 AAC                         |

|     |      |             | 1110100: MPEG-4 AAC                         |

|     |      |             | 0010101: Enhanced AC-3                      |

|     |      |             | 0010110: MAT                                |

|     |      |             | others: reserved                            |

### SPDIF\_REPETTION

Address: Operational Base + offset (0x0104) Channel Repetition Register

| Bit   | Attr | Reset Value | Description                                |

|-------|------|-------------|--------------------------------------------|

| 31:16 | RO   | 0x0         | reserved                                   |

| 15:0  | RW   | 0×0000      | REPETTION                                  |

|       |      |             | Repetition                                 |

|       |      |             | This define the repetition period when the |

|       |      |             | channel conveys non-linear PCM             |

#### SPDIF\_BURTSINFO\_SHD

Address: Operational Base + offset (0x0108) Shadow Channel Burst Info Register

F

| Bit     | Attr | Reset Value | Description                                       |

|---------|------|-------------|---------------------------------------------------|

|         |      |             | PD                                                |

| 31:16   |      | 0x0000      | pd • • • •                                        |

|         | RO   |             | Preamble Pd for non-linear pcm, indicating the    |

|         |      |             | length of burst payload in unit of bytes or bits. |

|         |      |             | BSNUM                                             |

| 15:13 R |      | 0×0         | Bitstream Number                                  |

|         | RU   |             | This field indicates the bitstream number.        |

|         |      |             | Usually the birstream number is 0.                |

|         |      |             | DATAINFO                                          |

| 12:8    | RO   | 0x00        | Data-type-dependent info                          |

|         |      |             | This field gives the data-type-dependent info     |

|         |      | RO 0x0      | ERRFLAG                                           |

|         |      |             | Error Flag                                        |

| 7       |      |             | 0: indicates a valid burst-payload                |

| /       | RU   |             | 1: indicates that the burst-payload may           |

|         |      |             | contain errors                                    |

|         |      |             |                                                   |

| Bit                    | Attr      | Reset Value | Description                                 |

|------------------------|-----------|-------------|---------------------------------------------|

|                        |           |             | DATATYPE                                    |

|                        |           |             | Data type                                   |

|                        |           |             | 0000000: null data                          |

|                        |           |             | 0000001: AC-3 data                          |

|                        |           |             | 0000011: Pause data                         |

|                        |           |             | 0000100: MPEG-1 layer 1 data                |

|                        |           |             | 0000101: MPEG-1 layer 2 or 3 data or MPEG-2 |

|                        |           |             | without extension                           |

|                        |           |             | 0000110: MPEG-2 data with extension         |

|                        |           |             | 0000111: MPEG-2 AAC                         |

|                        |           |             | 0001000: MPEG-2, layer-1 low sampling       |

|                        |           |             | frequency                                   |

|                        |           |             | 0001001: MPEG-2, layer-2 low sampling       |

|                        |           |             | frequency                                   |

|                        |           |             | 0001010: MPEG-2, layer-3 low sampling       |

|                        |           |             | frequency                                   |

|                        |           |             | 0001011: DTS type I                         |

|                        |           |             | 0001100: DTS type II                        |

|                        |           |             | 0001101: DTS type III                       |

|                        |           |             | 0001110: ATRAC                              |

| 6:0                    | RO        | 0x00        | 0001111: ATRAC 2/3                          |

| 0.0                    | KU        | 0,00        | 0010000: ATRAC-X                            |

|                        |           |             | 0010001: DTS type IV                        |

|                        |           |             | 0010010: WMA professional type I            |

|                        |           |             | 0110010: WMA professional type II           |

|                        |           | • . <       | 1010010: WMA professional type III          |

|                        |           |             | 1110010: WMA professional type IV           |

|                        |           |             | 0010011: MPEG-2 AAC low sampling            |

|                        |           |             | frequency                                   |

|                        |           |             | 0110011: MPEG-2 AAC low sampling            |

|                        |           |             | frequency                                   |

|                        |           |             | 1010011: MPEG-2 AAC low sampling            |

|                        | $\bigcap$ |             | frequency                                   |

| $\boldsymbol{\lambda}$ |           |             | 1110011: MPEG-2 AAC low sampling            |

|                        |           |             | frequency                                   |

| <b>y</b>               |           |             | 0010100: MPEG-4 AAC                         |

|                        |           |             | 0110100: MPEG-4 AAC                         |

|                        |           |             | 1010100: MPEG-4 AAC                         |

|                        |           |             | 1110100: MPEG-4 AAC                         |

|                        |           |             | 0010101: Enhanced AC-3                      |

|                        |           |             | 0010110: MAT                                |

|                        |           |             | others: reserved                            |

#### SPDIF\_REPETTION\_SHD

Address: Operational Base + offset (0x010c) Shadow Channel Repetition Register

| Bit   | Attr | Attr Reset Value Description |                                               |

|-------|------|------------------------------|-----------------------------------------------|

| 31:16 | RO   | 0x0                          | reserved                                      |

|       | RO   | 0×0000                       | REPETTION                                     |

|       |      |                              | Repetition                                    |

|       |      |                              | This register provides the repetition of the  |

|       |      |                              | bitstream when channel conveys non-linear     |

| 15:0  |      |                              | PCM. In the design, it is define the length   |

|       |      |                              | bwtween Pa of the two consecutive             |

|       |      |                              | data-burst. For the same audio format, the    |

|       |      |                              | definition is different. Please convert the   |

|       |      |                              | actual repetition in order to comply with the |

|       |      |                              | design.                                       |

#### SPDIF\_USRDR\_SHDn

Address: Operational Base + offset (0x0190) Shadow User Data Register n

| Bit   | Attr | Reset Value | Description                  |

|-------|------|-------------|------------------------------|

|       |      |             | USR_SUB_1                    |

| 31:16 | RO   | 0x0000      | User Data Subframe 1         |

|       |      |             | User Data Bit for Subframe 1 |

|       |      |             | USR_SUB_0                    |

| 15:0  | RO   | 0x0000      | User Data Subframe 0         |

|       |      |             | User Data Bit for Subframe 0 |

# 17.5 Interface description

#### Table 17-1 IOMUX Setting

|                    |   | Table 17-1 IOMOX Se  | ung                      |

|--------------------|---|----------------------|--------------------------|

| Module Pin IO      |   | Pad Name             | IOMUX Setting            |

| spdif_tx           | 0 | SPDIFtx_AUDIOgpio6b3 | GPIO6B_IOMUX[7:6]= 2'b01 |

| Notes: 1. O=output |   |                      |                          |

# **17.6 Application Notes**

## 17.6.1 Channel Status Bit and Validity Flag Bit

Normally the channel status bits and validity flag bits are not necessarily updated frequently. If it is desired to change the channel status bits or validity flag, please write to the corresponding register after a block terminate interrupt is asserted. The new value will take effect immediately.

## 17.6.2 User Data Bit

As the user data bits are updated frequently, the design takes use of the shadow register mechanism to store and convey the user data bit. When the SPDIF interface is disabled, the values of the shadow user data registers keeps the same with the corresponding user data registers. After the SPDIF starts, any change of the user data register will not go to the corresponding shadow user data registers until an user data interrupt is asserted.

Therefore before the SPDIF transfer starts, prepare the first 384 user data bits by writing them to the SPDIF\_USRDR registers. After the SPDIF transfer starts, writing the second 384

user data bits to the SPDIF\_USRDR registers. Then wait for the assertion of user data interrupt. The second 384 user data bits goes to the shadow registers, and then third 384 user bits are written to SPDIF\_USRDR.

## 17.6.3 Burst Info and Repetition

The shadow register mechanism is also applied to the data of burst info and repetition as the user data. The difference is that the update of shadow register will be taken after assertion of the block terminate interrupt.

It is important to note that the repetition defined in the design is a little different from the repetition defined in IEC-61957. The repetition is always defined as the length (measured in IEC-60958 frame) between Pa of two consecutive data-bursts. Therefore the user needs to calculation the new repetition value if the definition of the repetition is different for some audio formats such as AC-3.