# **Chapter 42 Serial Peripheral Interface (SPI)**

#### **42.1 Overview**

The serial peripheral interface is an APB slave device. A four wire full duplex serial protocol from Motorola. There are four possible combinations for the serial clock phase and polarity. The clock phase (SCPH) determines whether the serial transfer begins with the falling edge of slave select signals or the first edge of the serial clock. The slave select line is held high when the SPI is idle or disabled. This SPI controller can work as either master or slave mode.

SPI Controller supports the following features:

- Support Motorola SPI, TI Synchronous Serial Protocol and National Semiconductor Microwire interface

- Support 32-bit APB bus

- Support two internal 16-bit wide and 32-location deep FIFOs, one for transmitting and the other for receiving serial data

- Support two chip select signals in master mode

- Support 4, 8, 16 bit serial data transfer

- Support configurable interrupt polarity

- Support asynchronous APB bus and SPI clock

- Support master and slave mode

- Support DMA handshake interface and configurable DMA water level

- Support transmit FIFO empty, underflow, receive FIFO full, overflow, interrupt and all interrupts can be masked

- Support configurable water level of transmit FIFO empty and receive FIFO full interrupt

- Support combine interrupt output

- Support up to half of SPI clock frequency transfer in master mode and one sixth of SPI clock frequency transfer in slave mode

- Support full and half duplex mode transfer

- Stop transmitting SCLK if transmit FIFO is empty or receive FIFO is full in master mode

- Support configurable delay from chip select active to SCLK active in master mode

- Support configurable period of chip select inactive between two parallel data in master mode

- Support big and little endian, MSB and LSB first transfer

- Support two 8-bit audio data store together in one 16-bit wide location

- Support sample RXD 0~3 SPI clock cycles later

- Support configurable SCLK polarity and phase

- Support fix and incremental address access to transmit and receive FIFO

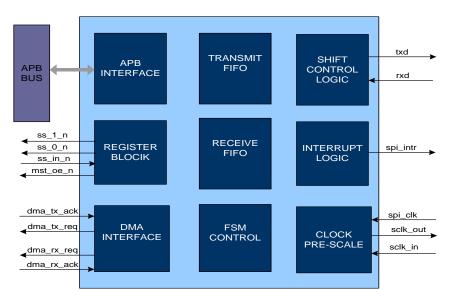

# 42.2 Block Diagram

The SPI Controller comprises with:

- AMBA APB interface and DMA Controller Interface

- Transmit and receive FIFO controllers and an FSM controller

- Register block

- Shift control and interrupt

Fig. 42-1 SPI Controller Block diagram

#### **APB INTERFACE**

The host processor accesses data, control, and status information on the SPI through the APB interface. The SPI supports APB data bus widths of 8, 16, and 32 bits.

#### **DMA INTERFACE**

This block has a handshaking interface to a DMA Controller to request and control transfers. The APB bus is used to perform the data transfer to or from the DMA Controller.

#### **FIFO LOGIC**

For transmit and receive transfers, data transmitted from the SPI to the external serial device is written into the transmit FIFO. Data received from the external serialdevice into the SPI is pushed into the receive FIFO. Both fifos are 32x16bits.

#### **FSM CONTROL**

Control the state's transformation of the design.

#### **REGISTER BLOCK**

All registers in the SPI are addressed at 32-bit boundaries to remain consistent with the AHB bus. Where the physical size of any register is less than 32-bits wide, the upper unused bits of the 32-bit boundary are reserved. Writing to these bits has no effect; reading from these bits returns 0.

#### SHIFT CONTROL

Shift control logic shift the data from the transmit fifo or to the receive fifo. This logic automatically right-justifies receive data in the receive FIFO buffer.

#### **INTERRUPT CONTROL**

The SPI supports combined and individual interrupt requests, each of which can be masked. The combined interrupt request is the ORed result of all other SPI interrupts after masking.

# 42.3 Function description

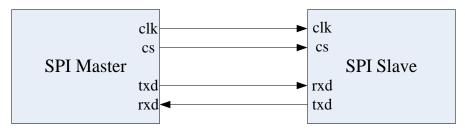

Fig. 42-2 SPI Master and Slave Interconnection

The SPI controller support dynamic switching between master and slave in a system. The diagram show how the SPI controller connects with other SPI devices.

#### **Operation Modes**

The SPI can be configured in the following two fundamental modes of operation: Master Mode when SPI\_CTRLR0 [20] is 1'b0, Slave Mode when SPI\_CTRLR0 [20] is 1'b1.

#### **Transfer Modes**

The SPI operates in the following three modes when transferring data on the serial bus.

#### 1. Transmit and Receive

When SPI\_CTRLR0 [19:18] == 2'b00, both transmit and receive logic are valid.

#### 2. Transmit Only

When SPI\_CTRLR0 [19:18] == 2'b01, the receive data are invalid and should not be stored in the receive FIFO.

#### 3. Receive Only

When SPI\_CTRLR0 [19:18] == 2'b10, the transmit data are invalid.

#### **Clock Ratios**

A summary of the frequency ratio restrictions between the bit-rate clock (sclk\_out / sclk\_in) and the SPI peripheral clock (spi\_clk) are described as,

When SPI Controller works as master, the  $F_{spi\ clk} > = 2 \times (maximum\ F_{sclk}\ out)$

When SPI Controller works as slave, the  $F_{spi}$  clk >= 6 × (maximum  $F_{sclk}$  in)

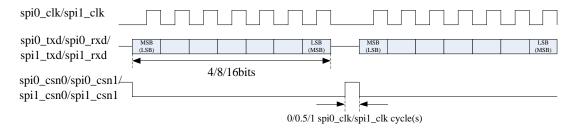

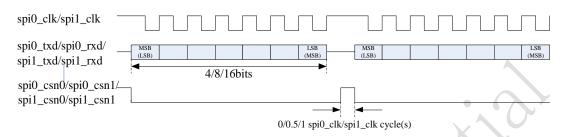

With the SPI, the clock polarity (SCPOL) configuration parameter determines whether the inactive state of the serial clock is high or low. To transmit data, both SPI peripherals must have identical serial clock phase (SCPH) and clock polarity (SCPOL) values. The data frame can be 4/8/16 bits in length.

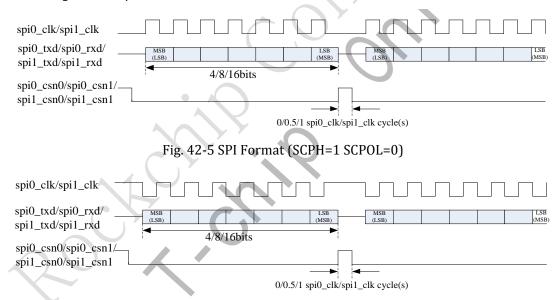

When the configuration parameter SCPH = 0, data transmission begins on the falling edge of the slave select signal. The first data bit is captured by the master and slave peripherals on the first edge of the serial clock; therefore, valid data must be present on the txd and rxd lines prior to the first serial clock edge. The following two figures show a timing diagram for a single SPI data transfer with SCPH = 0. The serial clock is shown for configuration parameters SCPOL = 0 and SCPOL = 1.

Fig. 42-3 SPI Format (SCPH=0 SCPOL=0)

Fig. 42-4 SPI Format (SCPH=0 SCPOL=1)

When the configuration parameter SCPH = 1, both master and slave peripherals begin transmitting data on the first serial clock edge after the slave select line is activated. The first data bit is captured on the second (trailing) serial clock edge. Data are propagated by the master and slave peripherals on the leading edge of the serial clock. During continuous data frame transfers, the slave select line may be held active-low until the last bit of the last frame has been captured. The following two figures show the timing diagram for the SPI format when the configuration parameter SCPH = 1.

Fig. 42-6 SPI Format (SCPH=1 SCPOL=1)

# **42.4 Register Description**

This section describes the control/status registers of the design. Pay attention that there are two SPI controllers in the chip: spi0 & spi1, so the base address in the following register

descriptions can be either spi0 or spi1 base address.

## **42.4.1 Registers Summary**

| Name        | Offset            | Size | Reset Value | Description                     |

|-------------|-------------------|------|-------------|---------------------------------|

| SPI_CTRLR0  | 0x0000            | W    | 0x00000002  | Control Register 0              |

| SPI_CTRLR1  | 0x0004            | W    | 0x00000000  | Control Register 1              |

| SPI_ENR     | 0x0008            | W    | 0x00000000  | SPI Enable                      |

| SPI_SER     | 0x000c            | W    | 0x00000000  | Slave Enable Register           |

| SPI_BAUDR   | 0x0010            | W    | 0x0000000   | Baud Rate Select                |

| SPI_TXFTLR  | 0x0014            | W    | 0x00000000  | Transmit FIFO Threshold Level   |

| SPI_RXFTLR  | 0x0018            | W    | 0×00000000  | Receive FIFO Threshold<br>Level |

| SPI_TXFLR   | 0x001c            | W    | 0x00000000  | Transmit FIFO Level             |

| SPI_RXFLR   | 0x0020            | W    | 0x00000000  | Receive FIFO Level              |

| SPI_SR      | 0x0024            | W    | 0x000000c   | SPI Status                      |

| SPI_IPR     | 0x0028            | W    | 0x00000000  | Interrupt Polarity              |

| SPI_IMR     | 0x002c            | W    | 0x00000000  | Interrupt Mask                  |

| SPI_ISR     | 0x0030            | W    | 0x00000000  | Interrupt Status                |

| SPI_RISR    | 0x0034            | W    | 0x0000001   | Raw Interrupt Status            |

| SPI_ICR     | 0x0038            | W    | 0x00000000  | Interrupt Clear                 |

| SPI_DMACR   | 0x003c            | W    | 0x00000000  | DMA Control                     |

| SPI_DMATDLR | 0x0040            | W    | 0x00000000  | DMA Transmit Data Level         |

| SPI_DMARDLR | 0x0044            | W    | 0x00000000  | DMA Receive Data Level          |

| SPI_TXDR    | 0x0400~<br>0x07fc | W    | 0x00000000  | Transmit FIFO Data              |

| SPI_RXDR    | 0x0800~<br>0x0bfc | W    | 0x00000000  | Receive FIFO Data               |

Notes: <u>Size</u>: **B**-Byte (8 bits) access, **HW**-Half WORD (16 bits) access, **W**-WORD (32 bits) access

# 42.4.2 Detail Register Description

## SPI\_CTRLR0

Address: Operational Base + offset (0x0000)

Control Register 0

| Bit   | Attr | Reset Value                                | Description             |

|-------|------|--------------------------------------------|-------------------------|

| 31:22 | RO   | 0x0                                        | reserved                |

|       |      | MTM                                        |                         |

|       |      |                                            | Microwire Transfer Mode |

| 21 RW | 0x0  | Valid when frame format is set to National |                         |

|       |      | Semiconductors Microwire.                  |                         |

|       |      | 1'b0: non-sequential transfer              |                         |

|       |      | 1'b1: sequential transfer                  |                         |

| Bit   | Attr   | Reset Value | Description                                     |

|-------|--------|-------------|-------------------------------------------------|

|       |        |             | ОРМ                                             |

| 20    | DW     | 0.40        | Operation Mode                                  |

| 20    | RW     | 0x0         | 1'b0: Master Mode                               |

|       |        |             | 1'b1: Slave Mode                                |

|       |        |             | XFM                                             |

|       |        |             | Transfer Mode                                   |

| 19:18 | RW     | 0×0         | 2'b00 :Transmit & Receive                       |

| 19.10 | KVV    | UXU         | 2'b01 : Transmit Only                           |

|       |        |             | 2'b10 : Receive Only                            |

|       |        |             | 2'b11 :reserved                                 |

|       |        |             | FRF                                             |

|       |        |             | Frame Format                                    |

| 17:16 | RW     | 0x0         | 2'b00: Motorola SPI                             |

| 17.10 |        | OXO         | 2'b01: Texas Instruments SSP                    |

|       |        |             | 2'b10: National Semiconductors Microwire        |

|       |        |             | 2'b11 : Reserved                                |

|       |        |             | RSD                                             |

|       |        |             | Rxd Sample Delay                                |

|       |        |             | When SPI is configured as a master, if the rxd  |

|       |        |             | data cannot be sampled by the sclk_out edge     |

|       |        |             | at the right time, this register should be      |

|       |        |             | configured to define the number of the spi_clk  |

| 15:14 | RW     | 0x0         | cycles after the active sclk_out edge to        |

|       |        |             | sample rxd data later when SPI works at high    |

|       |        |             | frequency.                                      |

|       |        | A           | 2'b00:do not delay                              |

|       |        |             | 2'b01:1 cycle delay                             |

|       |        |             | 2'b10:2 cycles delay                            |

|       |        | 1 0         | 2'b11:3 cycles delay BHT                        |

|       |        |             | Byte and Halfword Transform                     |

| 13    | RW     | 0x0         | Valid when data frame size is 8bit.             |

| 13    | IXVV   | UXU         | 1'b0: apb 16bit write/read, spi 8bit write/read |

|       | $\cup$ |             | 1'b1: apb 8bit write/read, spi 8bit write/read  |

|       |        |             | FBM                                             |

| 7     |        |             | First Bit Mode                                  |

| 12    | RW     | 0x0         | 1'b0: first bit is MSB                          |

|       |        |             | 1'b1: first bit is LSB                          |

|       |        |             | EM                                              |

|       |        |             | Endian Mode                                     |

|       | DIA    |             | Serial endian mode can be configured by this    |

| 11    | RW     | 0x0         | bit. Apb endian mode is always little endian.   |

|       |        |             | 1'b0: little endian                             |

|       |        |             | 1'b1: big endian                                |

| Bit | Attr | Reset Value | Description                                         |

|-----|------|-------------|-----------------------------------------------------|

|     |      |             | SSD                                                 |

|     |      |             | ss_n to sclk_out delay                              |

|     |      |             | Valid when the frame format is set to Motorola      |

| 10  | RW   | 0×0         | SPI and SPI used as a master.                       |

| 10  | KVV  | UXU         | 1'b0: the period between ss_n active and            |

|     |      |             | sclk_out active is half sclk_out cycles.            |

|     |      |             | 1'b1: the period between ss_n active and            |

|     |      |             | sclk_out active is one sclk_out cycle.              |

|     |      |             | CSM                                                 |

|     |      |             | Chip Select Mode                                    |

|     |      |             | Valid when the frame format is set to Motorola      |

|     |      |             | SPI and SPI used as a master.                       |

|     |      |             | 2'b00: ss_n keep low after every frame data is      |

| 9:8 | RW   | 0x0         | transferred.                                        |

|     |      |             | 2'b01: ss_n be high for half sclk_out cycles        |

|     |      |             | after every frame data is transferred.              |

|     |      |             | 2'b10: ss_n be high for one sclk_out cycle          |

|     |      |             | after every frame data is transferred.              |

|     |      |             | 2'b11: reserved                                     |

|     |      | 0×0         | SCPOL                                               |

|     |      |             | Serial Clock Polarity                               |

| 7   | RW   |             | Valid when the frame format is set to Motorola      |

|     |      |             | SPI.                                                |

|     |      |             | 1'b0: Inactive state of serial clock is low         |

|     |      |             | 1'b1: Inactive state of serial clock is high        |

|     |      | A           | SCPH                                                |

| 6   |      |             | Serial Clock Phase                                  |

|     |      |             | Valid when the frame format is set to Motorola SPI. |

|     | RW   | 0×0         | 1'b0: Serial clock toggles in middle of first       |

|     |      |             | data bit                                            |

|     |      |             | 1'b1: Serial clock toggles at start of first data   |

|     |      |             | bit                                                 |

|     | V )  |             | טונ                                                 |

| Bit            | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Bit</b> 5:2 | RW   | 0x0         | CFS Control Frame Size Selects the length of the control word for the Microwire frame format. 4'b0000~4'b0010: reserved 4'b0011: 4-bit serial data transfer 4'b0100: 5-bit serial data transfer 4'b0101: 6-bit serial data transfer 4'b0110: 7-bit serial data transfer 4'b0111: 8-bit serial data transfer 4'b1000: 9-bit serial data transfer 4'b1001: 10-bit serial data transfer 4'b1010: 11-bit serial data transfer 4'b1011: 12-bit serial data transfer 4'b1101: 13-bit serial data transfer 4'b1101: 15-bit serial data transfer |

|                |      |             | 4'b1111: 16-bit serial data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1:0            | RW   | 0x2         | DFS Data Frame Size Selects the data frame length. 2'b00: 4bit data 2'b01: 8bit data 2'b10: 16bit data 2'b11: reserved                                                                                                                                                                                                                                                                                                                                                                                                                   |

## SPI\_CTRLR1

Address: Operational Base + offset (0x0004)

Control Register 1

| Bit     | Attr   | Reset Value                                 | Description                                    |

|---------|--------|---------------------------------------------|------------------------------------------------|

| 31:16   | RO     | 0x0                                         | reserved                                       |

|         |        |                                             | NDM                                            |

|         |        |                                             | Number of Data Frames                          |

|         |        |                                             | When Transfer Mode is receive only, this       |

|         |        |                                             | register field sets the number of data frames  |

| 15:0 RW | 0x0000 | to be continuously received by the SPI. The |                                                |

| 15.0    |        | 00000                                       | SPI continues to receive serial data until the |

|         |        |                                             | number of data frames received is equal to     |

|         |        |                                             | this register value plus 1, which enables you  |

|         |        |                                             | to receive up to 64 KB of data in a continuous |

|         |        |                                             | transfer.                                      |

## SPI\_ENR

Address: Operational Base + offset (0x0008)

SPI Enable

| Bit  | Attr | Reset Value | Description                                   |

|------|------|-------------|-----------------------------------------------|

| 31:1 | RO   | 0x0         | reserved                                      |

|      |      |             | ENR                                           |

|      |      |             | SPI Enable                                    |

| 0    | RW   | 0x0         | Enables and disables all SPI operations.      |

|      |      |             | Transmit and receive FIFO buffers are cleared |

|      |      |             | when the device is disabled.                  |

## SPI\_SER

Address: Operational Base + offset (0x000c)

Slave Enable Register

| Tradic Register |        |                                         |             |

|-----------------|--------|-----------------------------------------|-------------|

| Bit             | Attr   | Reset Value                             | Description |

| 31:2            | RO     | 0x0                                     | reserved    |

| 1:0 RW          | W IOXO | SER                                     |             |

|                 |        | Slave Select Enable                     |             |

|                 |        | This register is valid only when SPI is |             |

|                 |        | configured as a master device.          |             |

## SPI\_BAUDR

Address: Operational Base + offset (0x0010)

Baud Rate Select

| Rate Sele | -    | 1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 31:16     | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15:0      | RW   | 0×0000      | BAUDR Baud Rate Select SPI Clock Divider. This register is valid only when the SPI is configured as a master device. The LSB for this field is always set to 0 and is unaffected by a write operation, which ensures an even value is held in this register. If the value is 0, the serial output clock (sclk_out) is disabled. The frequency of the sclk_out is derived from the following equation: Fsclk_out = Fspi_clk/ SCKDV Where SCKDV is any even value between 2 and 65534. For example: for Fspi_clk = 3.6864MHz and SCKDV = 2 Fsclk_out = 3.6864/2= 1.8432MHz |

## SPI\_TXFTLR

Address: Operational Base + offset (0x0014)

Transmit FIFO Threshold Level

| Bit Attr Reset Value | Description |

|----------------------|-------------|

|----------------------|-------------|

| Bit  | Attr | Reset Value | Description                                    |

|------|------|-------------|------------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                       |

|      |      | TXFTLR      |                                                |

|      |      |             | Transmit FIFO Threshold Level                  |

| 4:0  | RW   | 0x00        | When the number of transmit FIFO entries is    |

|      |      |             | less than or equal to this value, the transmit |

|      |      |             | FIFO empty interrupt is triggered.             |

## SPI\_RXFTLR

Address: Operational Base + offset (0x0018)

Receive FIFO Threshold Level

| Bit  | Attr | Reset Value | Description                                  |

|------|------|-------------|----------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                     |

|      |      | RXFTLR      |                                              |

|      |      |             | Receive FIFO Threshold Level                 |

| 4:0  | RW   | 0x00        | When the number of receive FIFO entries is   |

|      |      |             | greater than or equal to this value + 1, the |

|      |      |             | receive FIFO full interrupt is triggered.    |

## SPI\_TXFLR

Address: Operational Base + offset (0x001c)

Transmit FIFO Level

| Bit  | Attr | Reset Value    | Description                                  |

|------|------|----------------|----------------------------------------------|

| 31:6 | RO   | 0x0            | reserved                                     |

| 5:0  |      | $10 \times 00$ | TXFLR                                        |

|      | RO   |                | Transmit FIFO Level                          |

|      |      |                | Contains the number of valid data entries in |

|      |      |                | the transmit FIFO.                           |

### SPI\_RXFLR

Address: Operational Base + offset (0x0020)

Receive FIFO Level

| Bit  | Attr | Reset Value | Description                                  |

|------|------|-------------|----------------------------------------------|

| 31:6 | RO   | 0x0         | reserved                                     |

| 5:0  | RO   | 0x00        | RXFLR                                        |

|      |      |             | Receive FIFO Level                           |

|      |      |             | Contains the number of valid data entries in |

|      |      |             | the receive FIFO.                            |

### SPI\_SR

Address: Operational Base + offset (0x0024)

SPI Status

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:5 | RO   | 0x0         | reserved    |

| Bit | Attr | Reset Value | Description                                      |

|-----|------|-------------|--------------------------------------------------|

|     |      |             | RFF                                              |

| 4   | RO   | 0×0         | Receive FIFO Full                                |

| 4   | KO   | UXU         | 1'b0: Receive FIFO is not full                   |

|     |      |             | 1'b1: Receive FIFO is full                       |

|     |      |             | RFE                                              |

| 3   | RO   | 0x1         | Receive FIFO Empty                               |

| 3   | KO   | UXI         | 1'b0: Receive FIFO is not empty                  |

|     |      |             | 1'b1: Receive FIFO is empty                      |

|     |      | 0x1         | TFE                                              |

| 2   | RO   |             | Transmit FIFO Empty                              |

| 2   | KO   |             | 1'b0: Transmit FIFO is not empty                 |

|     |      |             | 1'b1: Transmit FIFO is empty                     |

|     |      |             | TFF                                              |

| 1   | RO   | 0x0         | Transmit FIFO Full                               |

|     |      | KO UXU      | 1'b0: Transmit FIFO is not full                  |

|     |      |             | 1'b1: Transmit FIFO is full                      |

|     |      |             | BSF                                              |

|     |      |             | SPI Busy Flag                                    |

|     |      |             | When set, indicates that a serial transfer is in |

| 0   | RO   | 0×0         | progress; when cleared indicates that the SPI    |

|     |      |             | is idle or disabled.                             |

|     |      |             | 1'b0: SPI is idle or disabled                    |

|     |      |             | 1'b1: SPI is actively transferring data          |

## SPI\_IPR

Address: Operational Base + offset (0x0028)

Interrupt Polarity

| Bit  | Attr | Reset Value | Description                                   |

|------|------|-------------|-----------------------------------------------|

| 31:1 | RO   | 0x0         | reserved                                      |

|      |      |             | IPR                                           |

|      |      | Y C         | Interrupt Polarity                            |

| 0    | RW   | 0x0         | Interrupt Polarity Register                   |

|      |      |             | 1'b0: Active Interrupt Polarity Level is HIGH |

|      |      |             | 1'b1: Active Interrupt Polarity Level is LOW  |

## SPI\_IMR

Address: Operational Base + offset (0x002c)

Interrupt Mask

| Bit  | Attr | Reset Value | Description                                |

|------|------|-------------|--------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                   |

| 4    |      | 0x0         | RFFIM                                      |

|      | DVA  |             | Receive FIFO Full Interrupt Mask           |

|      | RW   |             | 1'b0: spi_rxf_intr interrupt is masked     |

|      |      |             | 1'b1: spi_rxf_intr interrupt is not masked |

| Bit | Attr | Reset Value | Description                                |

|-----|------|-------------|--------------------------------------------|

|     |      |             | RFOIM                                      |

| 3   | RW   | 0×0         | Receive FIFO Overflow Interrupt Mask       |

| 3   | KVV  | UXU         | 1'b0: spi_rxo_intr interrupt is masked     |

|     |      |             | 1'b1: spi_rxo_intr interrupt is not masked |

|     |      |             | RFUIM                                      |

| 2   | RW   | 0×0         | Receive FIFO Underflow Interrupt Mask      |

| 2   | KVV  |             | 1'b0: spi_rxu_intr interrupt is masked     |

|     |      |             | 1'b1: spi_rxu_intr interrupt is not masked |

|     |      |             | TFOIM                                      |

| 1   | RW   | 0x0         | Transmit FIFO Overflow Interrupt Mask      |

| 1   |      |             | 1'b0: spi_txo_intr interrupt is masked     |

|     |      |             | 1'b1: spi_txo_intr interrupt is not masked |

|     |      | 0x0         | TFEIM                                      |

| 0   | RW   |             | Transmit FIFO Empty Interrupt Mask         |

|     |      |             | 1'b0: spi_txe_intr interrupt is masked     |

|     |      |             | 1'b1: spi_txe_intr interrupt is not masked |

# SPI\_ISR

Address: Operational Base + offset (0x0030)

Interrupt Status

| Bit  | Attr | Reset Value | Description                                      |

|------|------|-------------|--------------------------------------------------|

| 31:5 | RO   | 0x0         | reserved                                         |

|      |      |             | RFFIS                                            |

|      |      |             | Receive FIFO Full Interrupt Status               |

| 4    | RO   | 0x0         | 1'b0: spi_rxf_intr interrupt is not active after |

| 7    | KO   | 0.00        | masking                                          |

|      |      |             | 1'b1: spi_rxf_intr interrupt is full after       |

|      |      |             | masking                                          |

|      |      | 1 U'.       | RFOIS                                            |

|      |      | 0×0         | Receive FIFO Overflow Interrupt Status           |

| 3    | RO   |             | 1'b0: spi_rxo_intr interrupt is not active after |

|      | NO - |             | masking                                          |

|      |      |             | 1'b1: spi_rxo_intr interrupt is active after     |

|      | _    |             | masking                                          |

|      |      |             | RFUIS                                            |

|      |      | 0×0         | Receive FIFO Underflow Interrupt Status          |

| 2    | RO   |             | 1'b0: spi_rxu_intr interrupt is not active after |

|      | NO.  |             | masking                                          |

|      |      |             | 1'b1: spi_rxu_intr interrupt is active after     |

|      |      |             | masking                                          |

| Bit | Attr | Reset Value | Description                                      |

|-----|------|-------------|--------------------------------------------------|

|     |      |             | TFOIS                                            |

|     |      |             | Transmit FIFO Overflow Interrupt Status          |

| 1   | RO   | 0×0         | 1'b0: spi_txo_intr interrupt is not active after |

| 1   | KU   | UXU         | masking                                          |

|     |      |             | 1'b1: spi_txo_intr interrupt is active after     |

|     |      |             | masking                                          |

|     |      | 0x0         | TFEIS                                            |

|     | RO   |             | Transmit FIFO Empty Interrupt Status             |

| 0   |      |             | 1'b0: spi_txe_intr interrupt is not active after |

|     |      |             | masking                                          |

|     |      |             | 1'b1: spi_txe_intr interrupt is active after     |

|     |      |             | masking                                          |

# SPI\_RISR

Address: Operational Base + offset (0x0034)

Raw Interrupt Status

| iterrupt Status |      |             |                                                  |

|-----------------|------|-------------|--------------------------------------------------|

| Bit             | Attr | Reset Value | Description                                      |

| 31:5            | RO   | 0x0         | reserved                                         |

|                 |      |             | RFFRIS                                           |

|                 |      |             | Receive FIFO Full Raw Interrupt Status           |

| 4               | RO   | 0×0         | 1'b0: spi_rxf_intr interrupt is not active prior |

| -               | KO   | 0.00        | to masking                                       |

|                 |      |             | 1'b1: spi_rxf_intr interrupt is full prior to    |

|                 |      |             | masking                                          |

|                 |      |             | RFORIS                                           |

|                 |      | A           | Receive FIFO Overflow Raw Interrupt Status       |

| 3               | RO   | 0x0         | 1'b0: spi_rxo_intr interrupt is not active prior |

|                 | KO   |             | to masking                                       |

|                 |      |             | 1'b1: spi_rxo_intr interrupt is active prior to  |

|                 |      |             | masking                                          |

|                 | RO   | Y' C        | RFURIS                                           |

|                 |      | 0x0         | Receive FIFO Underflow Raw Interrupt Status      |

| 2               |      |             | 1'b0: spi_rxu_intr interrupt is not active prior |

|                 |      |             | to masking                                       |

|                 |      |             | 1'b1: spi_rxu_intr interrupt is active prior to  |

|                 |      |             | masking                                          |

|                 |      |             | TFORIS                                           |

| 1               |      |             | Transmit FIFO Overflow Raw Interrupt Status      |

|                 | RO   | 0×0         | 1'b0: spi_txo_intr interrupt is not active prior |

|                 |      |             | to masking                                       |

|                 |      |             | 1'b1: spi_txo_intr interrupt is active prior to  |

|                 |      |             | masking                                          |

| Bit | Attr | Reset Value | Description                                      |

|-----|------|-------------|--------------------------------------------------|

|     | RO   | 0×1         | TFERIS                                           |

|     |      |             | Transmit FIFO Empty Raw Interrupt Status         |

| 0   |      |             | 1'b0: spi_txe_intr interrupt is not active prior |

| U   |      |             | to masking                                       |

|     |      |             | 1'b1: spi_txe_intr interrupt is active prior to  |

|     |      |             | masking                                          |

#### SPI\_ICR

Address: Operational Base + offset (0x0038)

Interrupt Clear

| Bit  | Attr   | Reset Value                             | Description                             |

|------|--------|-----------------------------------------|-----------------------------------------|

| 31:4 | RO     | 0x0                                     | reserved                                |

|      |        |                                         | CTFOI                                   |

| 3    | wo     | 0×0                                     | Clear Transmit FIFO Overflow Interrupt  |

| 3    | VVO    | UXU                                     | Write 1 to Clear Transmit FIFO Overflow |

|      |        |                                         | Interrupt                               |

|      |        | O 0x0                                   | CRFOI                                   |

| 2    | wo     |                                         | Clear Receive FIFO Overflow Interrupt   |

| _    | VVO    |                                         | Write 1 to Clear Receive FIFO Overflow  |

|      |        |                                         | Interrupt                               |

|      |        | 0 0x0                                   | CRFUI                                   |

| 1    | wo     |                                         | Clear Receive FIFO Underflow Interrupt  |

| 1    | WO UXU | Write 1 to Clear Receive FIFO Underflow |                                         |

|      |        | Interrupt                               |                                         |

|      |        |                                         | CCI                                     |

| 0    | WO 0x0 | 0x0                                     | Clear Combined Interrupt                |

|      |        |                                         | Write 1 to Clear Combined Interrupt     |

## SPI\_DMACR

Address: Operational Base + offset (0x003c)

DMA Control

| Bit  | Attr | Reset Value | Description                 |  |  |

|------|------|-------------|-----------------------------|--|--|

| 31:2 | RO   | 0x0         | reserved                    |  |  |

|      | RW   | 0x0         | TDE                         |  |  |

| 1    |      |             | Transmit DMA Enable         |  |  |

| 1    |      |             | 1'b0: Transmit DMA disabled |  |  |

|      |      |             | 1'b1: Transmit DMA enabled  |  |  |

| 0    | RW   | 0x0         | RDE                         |  |  |

|      |      |             | Receive DMA Enable          |  |  |

|      |      |             | 1'b0: Receive DMA disabled  |  |  |

|      |      |             | 1'b1: Receive DMA enabled   |  |  |

## SPI\_DMATDLR

Address: Operational Base + offset (0x0040)

DMA Transmit Data Level

| Bit  | Attr | Reset Value | Description                                      |  |

|------|------|-------------|--------------------------------------------------|--|

| 31:5 | RO   | 0x0         | reserved                                         |  |

| 4:0  | RW   | 0x00        | TDL                                              |  |

|      |      |             | Transmit Data Level                              |  |

|      |      |             | This bit field controls the level at which a DMA |  |

|      |      |             | request is made by the transmit logic. It is     |  |

|      |      |             | equal to the watermark level; that is, the       |  |

|      |      |             | dma_tx_req signal is generated when the          |  |

|      |      |             | number of valid data entries in the transmit     |  |

|      |      |             | FIFO is equal to or below this field value, and  |  |

|      |      |             | Transmit DMA Enable (DMACR[1]) = 1.              |  |

## SPI\_DMARDLR

Address: Operational Base + offset (0x0044)

DMA Receive Data Level

| Bit  | Attr | Reset Value | Description                                      |  |

|------|------|-------------|--------------------------------------------------|--|

| 31:5 | RO   | 0x0         | reserved                                         |  |

|      |      |             | RDL                                              |  |

|      |      |             | Receive Data Level                               |  |

|      |      |             | This bit field controls the level at which a DMA |  |

|      |      |             | request is made by the receive logic. The        |  |

| 4:0  | RW   | 0x00        | watermark level = DMARDL+1; that is,             |  |

|      |      |             | dma_rx_req is generated when the number of       |  |

|      |      |             | valid data entries in the receive FIFO is equal  |  |

|      |      |             | to or above this field value + 1, and Receive    |  |

|      |      |             | DMA Enable(DMACR[0])=1.                          |  |

## SPI\_TXDR

Address: Operational Base + offset  $(0x0400 \sim 0x07fc)$

Transmit FIFO Data

| Bit   | Attr | Reset Value | Description                                    |

|-------|------|-------------|------------------------------------------------|

| 31:16 | RO   | 0x0         | reserved                                       |

| 15:0  | wo   | 0x0000      | TXDR                                           |

|       |      |             | Transimt FIFO Data Register.                   |

|       |      |             | When it is written to, data are moved into the |

|       |      |             | transmit FIFO.                                 |

## SPI\_RXDR

Address: Operational Base + offset (0x0800~0x0bfc)

Receive FIFO Data

| Bit   | Attr | Reset Value | Description                                    |  |

|-------|------|-------------|------------------------------------------------|--|

| 31:16 | RO   | 0x0         | reserved                                       |  |

| 15:0  | RW   | 0x0000      | RXDR                                           |  |

|       |      |             | Receive FIFO Data Register.                    |  |

|       |      |             | When the register is read, data in the receive |  |

|       |      |             | FIFO is accessed.                              |  |

# 42.5 Interface description

Table 42-1 SPI interface description

| <b>Module Pin</b> | Direction | Pad Name                   | IOMUX Setting  |

|-------------------|-----------|----------------------------|----------------|

| spi0_clk          | I/O       | IO_SPI0clk_TS0data4_UAR    | GRF GPIO5B IOM |

|                   |           | T4EXPctsn_BBgpio5b4        | UX[9:8]=01     |

| spi0_csn0         | I/O       | IO_SPI0csn0_TS0data5_U     | GRF_GPIO5B_IOM |

|                   |           | ART4EXPrtsn_BBgpio5b5      | UX[11:10]=01   |

| spi0_txd          | 0         | IO_SPI0txd_TS0data6_UA     | GRF_GPIO5B_IOM |

|                   |           | RT4EXPsout_BBgpio5b6       | UX[13:12]=01   |

| spi0_rxd          | I         | IO_SPI0rxd_TS0data7_UA     | GRF_GPIO5B_IOM |

|                   |           | RT4EXPsin_BBgpio5b7        | UX[15:14]=01   |

| spi0_csn1         | 0         | IO_SPI0csn1_TS0sync_BB     | GRF_GPIO5C_IOM |

|                   |           | gpio5c0                    | UX[1:0]=01     |

| spi1_clk          | I/O       | IO_ISPshutteren_SPI1clk_   | GRF_GPIO7B_IOM |

|                   |           | GPIO30gpio7b4              | UX[9:8]=10     |

| spi1_csn0         | I/O       | IO_ISPflashtrigout_SPI1cs  | GRF_GPIO7B_IOM |

|                   |           | n0_GPIO30gpio7b5           | UX[11:10]=10   |

| spi1_rxd          | 0         | IO_ISPprelighttrig_SPI1rxd | GRF_GPIO7B_IOM |

|                   |           | _GPIO30gpio7b6             | UX[13:12]=10   |

| spi1_txd          | I         | IO_ISPshuttertrig_SPI1txd  | GRF_GPIO7B_IOM |

|                   |           | _GPIO30gpio7b7             | UX[15:14]=10   |

| spi2_clk          | I/O       | IO_SPI2clk_SCio_GPIO183    | GRF_GPIO8A_IOM |

|                   |           | 0gpio8a6                   | UX[13:12]=01   |

| spi2_csn0         | I/O       | IO_SPI2csn0_SCdetect_GP    | GRF_GPIO8A_IOM |

|                   |           | IO1830gpio8a7              | UX[15:14]=01   |

| spi2_rxd          | I         | IO_SPI2rxd_SCrst_GPIO18    | GRF_GPIO8B_IOM |

|                   |           | 30gpio8b0                  | UX[1:0]=01     |

| spi2_txd          | 0         | IO_SPI2txd_SCclk_GPIO18    | GRF_GPIO8B_IOM |

|                   |           | 30gpio8b1                  | UX[3:2]=01     |

| spi2_csn1         | 0         | IO_SPI2csn1_SCiot1_GPIO    | GRF_GPIO8A_IOM |

|                   |           | 1830gpio8a3                | UX[7:6]=01     |

Note: spi0\_csn1, spi1\_csn1,spi2\_csn1 can only be used in master mode

# **42.6 Application Notes**

#### **Clock Ratios**

A summary of the frequency ratio restrictions between the bit-rate clock (sclk\_out/sclk\_in) and the SPI peripheral clock (spi\_clk) are described as,

When SPI Controller works as master, the  $F_{spi\ clk} >= 2 \times (maximum\ F_{sclk}\ out)$

When SPI Controller works as slave, the  $F_{spi\_clk} >= 6 \times (maximum F_{sclk\_in})$

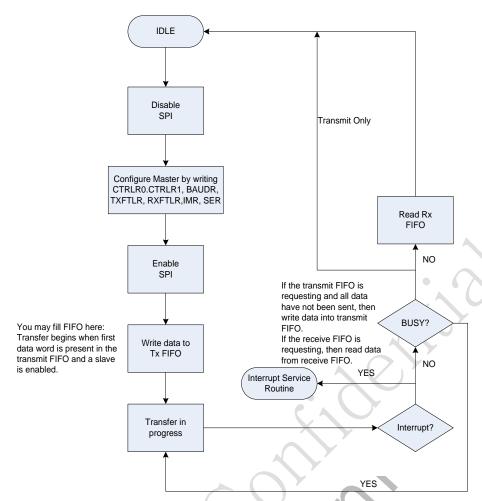

#### **Master Transfer Flow**

When configured as a serial-master device, the SPI initiates and controls all serial transfers. The serial bit-rate clock, generated and controlled by the SPI, is driven out on the sclk\_out line. When the SPI is disabled (SPI\_ENR = 0), no serial transfers can occur and sclk\_out is held in "inactive" state, as defined by the serial protocol under which it operates.

Fig. 42-7 SPI Master transfer flow diagram

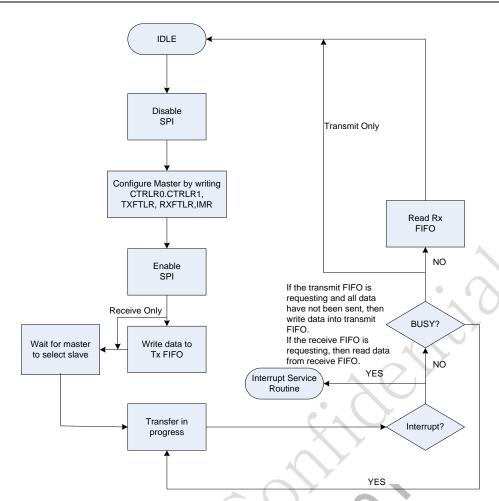

#### **Slave Transfer Flow**

When the SPI is configured as a slave device, all serial transfers are initiated and controlled by the serial bus master.

When the SPI serial slave is selected during configuration, it enables its txd data onto the serial bus. All data transfers to and from the serial slave are regulated on the serial clock line (sclk\_in), driven from the serial-master device. Data are propagated from the serial slave on one edge of the serial clock line and sampled on the opposite edge.

Fig. 42-8 SPI Slave transfer flow diagram