# **Chapter 50 WatchDog**

### 50.1 Overview

Watchdog Timer (WDT) is an APB slave peripheral that can be used to prevent system lockup that may be caused by conflicting parts or programs in a SoC. The WDT would generated interrupt or reset signal when it's counter reaches zero, then a reset controller would reset the system.

WDT supports the following features:

- 32 bits APB bus width

- WDT counter's clock is pclk

- 32 bits WDT counter width

- Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

- WDT can perform two types of operations when timeout occurs:

- Generate a system reset

- First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

- Programmable reset pulse length

- Total 16 defined-ranges of main timeout period

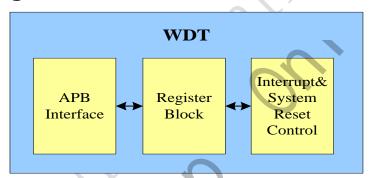

# 50.2 Block Diagram

Fig. 50-1 WDT block diagram

#### **Block Descriptions:**

#### **APB Interface**

The APB Interface implements the APB slave operation. It's data bus width is 32 bits.

#### **Register Block**

A register block that read coherence for the current count register.

### Interrupt & system reset control

An interrupt/system reset generation block comprising of a decrementing counter and control logic.

# 50.3 Function description

#### 50.3.1 Operation

#### **Counter**

The WDT counts from a preset (timeout) value in descending order to zero. When the counter reaches zero, depending on the output response mode selected, either a system reset or an

interrupt occurs. When the counter reaches zero, it wraps to the selected timeout value and continues decrementing. The user can restart the counter to its initial value. This is programmed by writing to the restart register at any time. The process of restarting the watchdog counter is sometimes referred as kicking the dog. As a safety feature to prevent accidental restarts, the value 0x76 must be written to the Current Counter Value Register (WDT\_CRR).

#### **Interrupts**

The WDT can be programmed to generate an interrupt (and then a system reset) when a timeout occurs. When a 1 is written to the response mode field (RMOD, bit 1) of the Watchdog Timer Control Register (WDT\_CR), the WDT generates an interrupt. If it is not cleared by the time a second timeout occurs, then it generates a system reset. If a restart occurs at the same time the watchdog counter reaches zero, an interrupt is not generated.

#### **System Resets**

When a 0 is written to the output response mode field (RMOD, bit 1) of the Watchdog Timer Control Register (WDT CR), the WDT generates a system reset when a timeout occurs.

#### **Reset Pulse Length**

The reset pulse length is the number of pclk cycles for which a system reset is asserted. When a system reset is generated, it remains asserted for the number of cycles specified by the reset pulse length or until the system is reset. A counter restart has no effect on the system reset once it has been asserted.

**Operation Flow Chart (Response mode=1)**

- 1. Select required timeout period.

- 2. Set reset pulse length, response mode, and enable WDT.

- 3. Write 0x76 to WDT\_CRR.

- 4. Starts back to selected timeout period.

- $5. \ Can \ clear \ by \ reading \ WDT\_EOI \ or \ restarting \ (kicking) \ the \ counter \ by \ writing \ 0x76 \ to \ WDT\_CRR.$

Fig. 50-2 WDT Operation Flow

# **50.4 Register Description**

This section describes the control/status registers of the design.

# 50.4.1 Registers Summary

| Name     | Offset | Size | Reset Value | Description                    |

|----------|--------|------|-------------|--------------------------------|

| WDT_CR   | 0x0000 | W    | 0x0000000a  | Control Register               |

| WDT_TORR | 0x0004 | W    | 0x0000000   | Timeout range Register         |

| WDT_CCVR | 0x0008 | W    | 0x0000000   | Current counter value Register |

| WDT_CRR  | 0x000c | W    | 0x0000000   | Counter restart Register       |

| WDT_STAT | 0x0010 | W    | 0x0000000   | Interrupt status Register      |

| WDT_EOI  | 0x0014 | W    | 0x00000000  | Interrupt clear Register       |

Notes: Size: B- Byte (8 bits) access, HW- Half WORD (16 bits) access, W-WORD (32 bits) access

# 50.4.2 Detail Register Description

#### WDT\_CR

Address: Operational Base + offset (0x0000)

Control Register

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:5 | RO   | 0x0         | reserved    |

| Bit | Attr | Reset Value | Description                                         |

|-----|------|-------------|-----------------------------------------------------|

|     |      |             | rst_pluse_lenth                                     |

|     |      |             | Reset pulse length.                                 |

|     |      |             | This is used to select the number of pclk cycles    |

|     |      |             | for which the system reset stays asserted.          |

|     |      |             | 3'b000: 2 pclk cycles                               |

| 4:2 | RW   | 0x2         | 3'b001: 4 pclk cycles                               |

| 7.2 |      | UNZ         | 3'b010: 8 pclk cycles                               |

|     |      |             | 3'b011: 16 pclk cycles                              |

|     |      |             | 3'b100: 32 pclk cycles                              |

|     |      |             | 3'b101: 64 pclk cycles                              |

|     |      |             | 3'b110: 128 pclk cycles                             |

|     |      |             | 3'b111: 256 pclk cycles                             |

|     |      |             | resp_mode                                           |

|     |      | 0×1<br>0×0  | Response mode.                                      |

|     |      |             | Selects the output response generated to a timeout. |

| 1   | RW   |             | 1'b0: Generate a system reset                       |

|     |      |             | 1'b1: First generate an interrupt and if it is not  |

|     |      |             | cleared by the time a second timeout occurs then    |

|     |      |             | generate a system reset                             |

|     |      |             | wdt_en                                              |

| 0   | RW   |             | WDT enable                                          |

|     |      |             | 1'b0: WDT disabled                                  |

|     |      |             | 1'b1: WDT enabled                                   |

# WDT\_TORR

Address: Operational Base + offset (0x0004)

Timeout range Register

| Bit  | Attr | Reset Value |          | Description |

|------|------|-------------|----------|-------------|

| 31:4 | RO   | 0x0         | reserved | <b>&gt;</b> |

| Bit | Attr | Reset Value | Description                                          |

|-----|------|-------------|------------------------------------------------------|

|     |      |             | timeout_period                                       |

|     |      |             | Timeout period.                                      |

|     |      |             | This field is used to select the timeout period from |

|     |      |             | which the watchdog counter restarts. A change of the |

|     |      |             | timeout period takes effect only after the next      |

|     |      |             | counter restart (kick).                              |

|     |      |             | The range of values available for a 32-bit watchdog  |

|     |      |             | counter are:                                         |

|     |      |             | 4'b0000: 0x0000ffff                                  |

|     |      |             | 4'b0001: 0x0001ffff                                  |

|     | RW   |             | 4'b0010: 0x0003ffff                                  |

| 3:0 |      | 0x0         | 4'b0011: 0x0007ffff                                  |

|     |      |             | 4'b0100: 0x000fffff                                  |

|     |      |             | 4'b0101: 0x001fffff                                  |

|     |      |             | 4'b0110: 0x003fffff                                  |

|     |      |             | 4'b0111: 0x007fffff                                  |

|     |      |             | 4'b1000: 0x00ffffff                                  |

|     |      |             | 4'b1001: 0x01ffffff                                  |

|     |      |             | 4'b1010: 0x03ffffff                                  |

|     |      |             | 4'b1011: 0x07ffffff                                  |

|     |      |             | 4'b1100: 0x0fffffff                                  |

|     |      |             | 4'b1101: 0x1fffffff                                  |

|     |      |             | 4'b1110: 0x3fffffff                                  |

|     |      |             | 4'b1111: 0x7fffffff                                  |

### WDT\_CCVR

Address: Operational Base + offset (0x0008)

Current counter value Register

| Bit  | Attr | Reset Value | Description                                           |

|------|------|-------------|-------------------------------------------------------|

|      |      |             | cur_cnt                                               |

|      |      |             | Current counter value                                 |

| 31:0 | RO   | 0x00000000  | This register, when read, is the current value of the |

|      |      |             | internal counter. This value is read coherently when  |

|      |      |             | ever it is read                                       |

### WDT\_CRR

Address: Operational Base + offset (0x000c)

Counter restart Register

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:8 | RO   | 0x0         | reserved    |

| Bit     | Attr | Reset Value | Description                                            |

|---------|------|-------------|--------------------------------------------------------|

|         |      | 0×00        | cnt_restart                                            |

| 7:0 W1C |      |             | Counter restart                                        |

|         | W1C  |             | This register is used to restart the WDT counter. As a |

|         | WIC  |             | safety feature to prevent accidental restarts, the     |

|         |      |             | value 0x76 must be written. A restart also clears the  |

|         |      |             | WDT interrupt. Reading this register returns zero.     |

### WDT\_STAT

Address: Operational Base + offset (0x0010)

Interrupt status Register

| Bit  | Attr | Reset Value | Description                                          |

|------|------|-------------|------------------------------------------------------|

| 31:1 | RO   | 0x0         | reserved                                             |

| 0 RO |      | 0×0         | wdt_status                                           |

|      | DO.  |             | This register shows the interrupt status of the WDT. |

|      | RU   |             | 1'b1: Interrupt is active regardless of polarity.    |

|      |      |             | 1'b0: Interrupt is inactive.                         |

### WDT\_EOI

Address: Operational Base + offset (0x0014)

Interrupt clear Register

| Bit  | Attr | Reset Value | Description                                     |

|------|------|-------------|-------------------------------------------------|

| 31:1 | RO   | 0x0         | reserved                                        |

| 0 R  |      | 0x0         | wdt_int_clr                                     |

|      | D.O. |             | Clears the watchdog interrupt.                  |

|      | RO   |             | This can be used to clear the interrupt without |

|      |      |             | restarting the watchdog counter.                |

# **50.5 Application Notes**

Please refer to the function description section.