# **Chapter 52 I2C Interface**

### 52.1 Overview

The Inter-Integrated Circuit (I2C) is a two wired (SCL and SDA), bi-directional serial bus that provides an efficient and simple method of information exchange between devices. This I2C bus controller supports master mode acting as a bridge between AMBA protocol and generic I2C bus system.

I2C Controller supports the following features:

- Item Compatible with I2C-bus

- AMBA APB slave interface

- Supports master mode of I2C bus

- Software programmable clock frequency and transfer rate up to 400Kbit/sec

- Supports 7 bits and 10 bits addressing modes

- Interrupt or polling driven multiple bytes data transfer

- Clock stretching and wait state generation

- There are two I2C controller in bus sub-system: I2C PMU, and I2C AUDIO. There are four I2C controller in peripheral sub-system: I2C SENSOR, I2C CAM, I2C\_TP, and I2C\_HDMI.

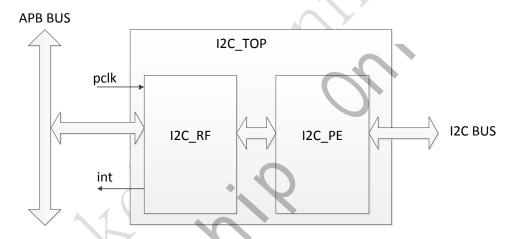

# 52.2 Block Diagram

Fig. 52-1 I2C architecture

### I2C\_RF

I2C\_RF module is used to control the I2C controller operation by the host with APB interface. It implements the register set and the interrupt functionality. The CSR component operates synchronously with the pclk clock.

### I2C\_PE

I2C\_PE module implements the I2C master operation for transmit data to and receive data from other I2C devices. The I2C master controller operates synchronously with the pclk.

### I2C\_TOP

I2C\_TOP module is the top module of the I2C controller.

# 52.3 Function description

This chapter provides a description about the functions and behavior under various conditions.

The I2C controller supports only Master function. It supports the 7-bits/10-bits addressing mode and support general call address. The maximum clock frequency and transfer rate can be up to 400Kbit/sec.

The operations of I2C controller is divided to 2 parts and described separately: initialization and master mode programming.

#### 52.3.1 Initialization

The I2C controller is based on AMBA APB bus architecture and usually is part of a SOC. So before I2C operates, some system setting & configuration must be conformed, which includes:

- I2C interrupt connection type: CPU interrupt scheme should be considered. If the I2C interrupt is connected to extra Interrupt Controller module, we need decide the INTC vector.

- I2C Clock Rate: The I2C controller uses the APB clock as the system clock so the APB clock will determine the I2C bus clock. The correct register setting is subject to the system requirement.

### **52.3.2 Master Mode Programming**

**1. SCL Clock**: When the I2C controller is programmed in Master mode, the SCL frequency is determine by I2C\_CLKDIV register. The SCL frequency is calculated by the following formula:

SCL Divisor = 8\*(CLKDIVL + 1 + CLKDIVH + 1)

SCL = PCLK/ SCLK Divisor

### 2. Data Receiver Register Access

When the i2c controller received MRXCNT bytes data. CPU can get the datas through register RXDATA0  $\sim$  RXDATA7. The controller can receive up to 32 byte data in one transaction.

When MRXCNT register is written, the I2C controller will start to drive SCL to receive data.

### 3. Transmit Trasmitter Register

Data to transmit are written to TXDATA0 $\sim$ 7 by CPU. The controller can transmit up to 32 byte data in one transaction. The lower byte will be transmitted first.

When MTXCNT register is written, the I2C controller will start to transmit data.

### 4. Start Command

Write 1 to I2C\_CON[3], the controller will send I2C start command.

### 5. Stop Command

Write 1 to I2C\_CON[4], the controller will send I2C stop command

#### 6. I2C Operation mode

There are four i2c operation modes.

When I2C\_CON[2:1] is 2'b00, the controller transmit all valid data in TXDATA0~TXDATA7 byte by byte. The controller will transmit lower byte first.

When I2C\_CON[2:1] is 2'b01, the controller will transmit device address in MRXADDR first (Write/Read bit = 0) and then transmit device register address in MRXRADDR. After that, the controller will assert restart signal and resend MRXADDR (Write/Read bit = 1). At last, the controller enter receive mode.

When I2C\_CON[2:1] is 2'b10, the controller is in receive mode, it will triggered clock to read MRXCNT byte data.

When I2C\_CON[2:1] is 2'b11, the controller will transmit device address in MRXADDR first (Write/Read bit = 1) and then transmit device register address in MRXRADDR. After that, the controller will assert restart signal and resend MRXADDR (Write/Read bit = 1). At last, the controller enter receive mode.

### 7. Read/Write Command

When I2C\_OPMODE(I2C\_CON[2:1]) is 2'b01 or 2'b11, the Read/Write command bit is decided by controller itself.

In RX only mode (I2C\_CON[2:1] is 2'b10), the Read/Write command bit is decided by MRXADDR[0].

In TX only mode (I2C\_CON[[2:1] is 2'b00), the Read/Write command bit is decided by TXDATA[0].

### 8. Master Interrupt Condition

There are 7 interrupt bits in I2C\_ISR register related to master mode.

Byte transmitted finish interrupt (Bit 0): The bit is asserted when Master complete transmitting a byte.

Byte received finish interrupt (Bit 1): The bit is asserted when Master complete receiving a byte.

MTXCNT bytes data transmitted finish interrupt (Bit 2): The bit is asserted when Master complete transmitting MTXCNT bytes.

MRXCNT bytes data received finish interrupt (Bit 3): The bit is asserted when Master complete receiving MRXCNT bytes.

Start interrupt (Bit 4): The bit is asserted when Master finish asserting start command to I2C bus.

Stop interrupt (Bit 5): The bit is asserted when Master finish asserting stop command to I2C bus.

NAK received interrupt (Bit 6): The bit is asserted when Master received a NAK handshake.

### 9. Last byte acknowledge control

If I2C\_CON[5] is 1, the I2C controller will transmit NAK handshake to slave when the last byte received in RX only mode.

If I2C\_CON[5] is 0, the I2C controller will transmit ACK handshake to slave when the last byte received in RX only mode.

# 10. How to handle nak handshake received

If I2C\_CON[6] is 1, the I2C controller will stop all transactions when NAK handshake received. And the software should take responsibility to handle the problem.

If I2C\_CON[6] is 0, the I2C controller will ignore all NAK handshake received.

#### 11. I2C controller data transfer waveform

#### Bit transferring

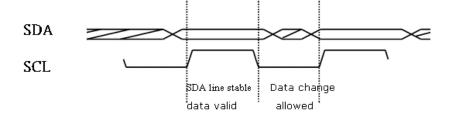

#### (a) Data Validity

The SDA line must be stable during the high period of SCL, and the data on SDA line can only be changed when SCL is in low state.

Fig. 52-2 I2C DATA Validity

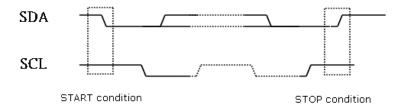

### (b) START and STOP conditions

START condition occurs when SDA goes low while SCL is in high period. STOP condition is generated when SDA line goes high while SCL is in high state.

Fig. 52-3 I2C Start and stop conditions

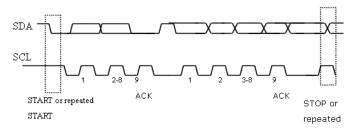

#### Data transfer

### (a) Acknowledge

After a byte of data transferring (clocks labeled as  $1\sim8$ ), in  $9^{th}$  clock the receiver must assert an ACK signal on SDA line, if the receiver pulls SDA line to low, it means "ACK", on the contrary, it's "NOT ACK".

Fig. 52-4 I2C Acknowledge

### (b) Byte transfer

The master own I2C bus might initiate multi byte to transfer to a slave. The transfer starts from a "START" command and ends in a "STOP" command. After every byte transfer, the receiver must reply an ACK to transmitter.

Fig. 52-5 I2C byte transfer

# **52.4 Register Description**

This section describes the control/status registers of the design.

# **52.4.1 Registers Summary**

| Name         | Offset | Size | Reset<br>Value | Description                                                 |

|--------------|--------|------|----------------|-------------------------------------------------------------|

| I2C_CON      | 0x0000 | W    | 0x0000000      | control register                                            |

| I2C_CLKDIV   | 0x0004 | W    | 0x00060006     | Clock divisor register                                      |

| I2C_MRXADDR  | 0x0008 | W    | 0x00000000     | the slave address accessed for master receive mode          |

| I2C_MRXRADDR | 0x000c | W    | 0x00000000     | the slave register address accessed for master recevie mode |

| I2C_MTXCNT   | 0x0010 | W    | 0x0000000      | master transmit count                                       |

| I2C_MRXCNT   | 0x0014 | W    | 0x0000000      | master receive count                                        |

| I2C_IEN      | 0x0018 | W    | 0x0000000      | interrupt enable register                                   |

| I2C_IPD      | 0x001c | W    | 0x0000000      | interrupt pending register                                  |

| I2C_FCNT     | 0x0020 | W    | 0x0000000      | finished count                                              |

| I2C_TXDATA0  | 0x0100 | W    | 0x0000000      | I2C transmit data register 0                                |

| I2C_TXDATA1  | 0x0104 | W    | 0x0000000      | I2C transmit data register 1                                |

| I2C_TXDATA2  | 0x0108 | W    | 0x0000000      | I2C transmit data register 2                                |

| I2C_TXDATA3  | 0x010c | W    | 0x0000000      | I2C transmit data register 3                                |

| I2C_TXDATA4  | 0x0110 | W    | 0x0000000      | I2C transmit data register 4                                |

| I2C_TXDATA5  | 0x0114 | W    | 0x0000000      | I2C transmit data register 5                                |

| I2C_TXDATA6  | 0x0118 | W    | 0x00000000     | I2C transmit data register 6                                |

| I2C_TXDATA7  | 0x011c | W    | 0x0000000      | I2C transmit data register 7                                |

| I2C_RXDATA0  | 0x0200 | W    | 0x0000000      | I2C receive data register 0                                 |

| I2C_RXDATA1  | 0x0204 | W    | 0x0000000      | I2C receive data register 1                                 |

| I2C_RXDATA2  | 0x0208 | W    | 0x0000000      | I2C receive data register 2                                 |

| I2C_RXDATA3  | 0x020c | W    | 0x0000000      | I2C receive data register 3                                 |

| I2C_RXDATA4  | 0x0210 | W    | 0x0000000      | I2C receive data register 4                                 |

| I2C_RXDATA5  | 0x0214 | W    | 0x0000000      | I2C receive data register 5                                 |

| I2C_RXDATA6  | 0x0218 | W    | 0x0000000      | I2C receive data register 6                                 |

| I2C_RXDATA7  | 0x021c | W    | 0x00000000     | I2C receive data register 7                                 |

Notes: Size: **B**- Byte (8 bits) access, **HW**- Half WORD (16 bits) access, **W**-WORD (32 bits) access

# **52.4.2 Detail Register Description**

# I2C\_CON

Address: Operational Base + offset (0x0000)

control register

| Bit  | Attr | Reset Value   | Description                              |

|------|------|---------------|------------------------------------------|

| 31:7 | RO   | 0x0           | reserved                                 |

|      |      | 00            | act2nak                                  |

| 6    | RW   |               | operation when NAK handshake is received |

| 6 KW | 0×0  | 1'b0: ignored |                                          |

|      |      |               | 1'b1: stop transaction                   |

| Bit | Attr  | Reset Value | Description                                            |

|-----|-------|-------------|--------------------------------------------------------|

|     |       |             | ack                                                    |

|     |       |             | last byte acknowledge control                          |

| 5   | RW    | 0x0         | last byte acknowledge control in master receive        |

| 3   | KVV   | UXU         | mode .                                                 |

|     |       |             | 1'b0: ACK                                              |

|     |       |             | 1'b1: NAK                                              |

|     |       |             | stop                                                   |

| 4   | W1C   | 0x0         | stop enable                                            |

| 4   | WIC   | UXU         | when this bit is written to 1, I2C will generate stop  |

|     |       |             | signal. It cleared itself when stop operation ends.    |

|     |       |             | start                                                  |

| 3   | W1C   | 0x0         | start enable                                           |

|     | WIC   | UXU         | when this bit is written to 1, I2C will generate start |

|     |       |             | signal. It cleared itself when start operation ends.   |

|     |       |             | i2c_mode                                               |

|     |       | 0x0         | 2'b00: transmit only                                   |

|     |       |             | 2'b01: transmit address (device + register address)    |

| 2:1 | RW    |             | > restart> transmit address -> receive only            |

| 2.1 | KVV   |             | 2'b10: receive only                                    |

|     |       |             | 2'b11: transmit address (device + register address,    |

|     |       |             | write/read bit is 1)> restart> transmit address        |

|     |       |             | (device address)> receive data                         |

| 0   | RW    | 0×0         | i2c_en                                                 |

| U   | IK VV |             | i2c module enable                                      |

# I2C\_CLKDIV

Address: Operational Base + offset (0x0004)

Clock divisor register

| Bit   | Attr | Reset Value | Description                           |

|-------|------|-------------|---------------------------------------|

|       |      |             | CLKDIVH                               |

| 31:16 | RW   | 0x0006      | SCL high level clock count            |

|       |      |             | $T(SCL_HIGH) = T(PCLK) * CLKDIVH * 8$ |

|       |      |             | CLKDIVL                               |

| 15:0  | RW   | 0x0006      | SCL low level clock count             |

|       |      |             | T (SCL_LOW) = T(PCLK) * CLKDIVL * 8   |

## I2C\_MRXADDR

Address: Operational Base + offset (0x0008)

the slave address accessed for master receive mode

| Bit   | Attr | Reset Value               | Description |

|-------|------|---------------------------|-------------|

| 31:27 | RO   | 0x0                       | reserved    |

| 26 RW | 0x0  | addhvld                   |             |

|       |      | address high byte valid   |             |

| 25 RW | 0x0  | addmvld                   |             |

|       |      | address middle byte valid |             |

| Bit    | Attr | Reset Value | Description                           |

|--------|------|-------------|---------------------------------------|

| 24 RW  | DW   | 0×0         | addlvld                               |

|        | KVV  |             | address low byte valid                |

| 23:0 R |      | 0x000000    | saddr                                 |

|        | RW   |             | master address register               |

|        |      |             | the lowest bit indicate write or read |

### I2C\_MRXRADDR

Address: Operational Base + offset (0x000c)

the slave register address accessed for master receive mode

| Bit   | Attr | Reset Value               | Description                     |

|-------|------|---------------------------|---------------------------------|

| 31:27 | RO   | 0x0                       | reserved                        |

| 26    | DW   | 0.40                      | sraddhvld                       |

| 26    | RW   | 0x0                       | address high byte valid         |

| 25 RW | 0x0  | sraddmvld                 |                                 |

|       |      | address middle byte valid |                                 |

| 24    | 24   | 0×0                       | sraddlvld                       |

| 24 RW | KVV  |                           | address low byte valid          |

| 23:0  | DW   | 0x000000                  | sraddr                          |

|       | KVV  |                           | slave register address accessed |

## I2C\_MTXCNT

Address: Operational Base + offset (0x0010)

master transmit count

| aoco. c.a. |      | J. 1 C      |                                 |

|------------|------|-------------|---------------------------------|

| Bit        | Attr | Reset Value | Description                     |

| 31:6       | RO   | 0x0         | reserved                        |

| 5:0        | RW   | 0x00        | mtxcnt<br>master transmit count |

## I2C\_MRXCNT

Address: Operational Base + offset (0x0014)

master receive count

| Bit    | Attr | Reset Value | Description          |

|--------|------|-------------|----------------------|

| 31:6   | RO   | 0x0         | reserved             |

| 5:0 RW | 0×00 | mrxcnt      |                      |

| 5.0    | I VV | 0.000       | master receive count |

### I2C\_IEN

Address: Operational Base + offset (0x0018)

interrupt enable register

| Bit  | Attr | Reset Value                             | Description |

|------|------|-----------------------------------------|-------------|

| 31:7 | RO   | 0x0                                     | reserved    |

| 6 RW | 0x0  | nakrcvien                               |             |

|      |      | NAK handshake received interrupt enable |             |

| Bit | Attr | Reset Value | Description                                    |

|-----|------|-------------|------------------------------------------------|

| Е   | DW   | 00          | stopien                                        |

| 5   | RW   | 0x0         | stop operation finished interrupt enable       |

| 4   | RW   | 0x0         | startien                                       |

| 4   | KVV  | UXU         | start operation finished interrupt enable      |

| 2   | RW   | 0x0         | mbrfien                                        |

| 3   | KVV  |             | MRXCNT data received finished interrupt enable |

| 2   | RW   | 0x0         | mbtfien                                        |

| 2   | RVV  |             | MTXCNT data transmit finished interrupt enable |

| 1   | RW   | / 0x0       | brfien                                         |

| 1   |      |             | byte receive finished interrupt enable         |

| 0   | DW   | 0.40        | btfien                                         |

| 0   | RW   | 0x0         | byte transmit finished interrupt enable        |

# I2C\_IPD

Address: Operational Base + offset (0x001c)

interrupt pending register

| Bit  | Attr | Reset Value | Description                                         |

|------|------|-------------|-----------------------------------------------------|

| 31:7 | RO   | 0x0         | reserved                                            |

| 6    | RW   | 0×0         | nakrcvipd                                           |

| U    | KVV  | UXU         | NAK handshake received interrupt pending bit        |

| 5    | RW   | 0×0         | stopipd                                             |

| 3    | KVV  | UXU         | stop operation finished interrupt pending bit       |

| 4    | RW   | 0x0         | startipd                                            |

| 4    | KVV  |             | start operation finished interrupt pending bit      |

| 3    | RW   | 0x0         | mbrfipd                                             |

| 3    | KVV  |             | MRXCNT data received finished interrupt pending bit |

| 2    | DW   | .W 0x0      | mbtfipd                                             |

| 2    | FCVV |             | MTXCNT data transmit finished interrupt pending bit |

| 1    | RW   | 0.0         | brfipd                                              |

| 1    |      | 0x0         | byte receive finished interrupt pending bit         |

| 0    | DW   | 0.00        | btfipd                                              |

| U    | 0 RW | 0x0         | byte transmit finished interrupt pending bit        |

# I2C\_FCNT

Address: Operational Base + offset (0x0020)

finished count

| Bit  | Attr | Reset Value | Description                                     |

|------|------|-------------|-------------------------------------------------|

| 31:6 | RO   | 0x0         | reserved                                        |

|      |      |             | fcnt                                            |

|      |      |             | finished count                                  |

| 5:0  | RW   | 0x00        | the count of data which has been transmitted or |

|      |      |             | received                                        |

|      |      |             | for debug purpose                               |

### I2C\_TXDATA0

Address: Operational Base + offset (0x0100)

I2C transmit data register 0

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RW   | 0x00000000  | txdata0     |

### I2C\_TXDATA1

Address: Operational Base + offset (0x0104)

I2C transmit data register 1

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RW   | 0x0000000   | txdata1     |

## I2C\_TXDATA2

Address: Operational Base + offset (0x0108)

I2C transmit data register 2

| Bit  | Attr | Reset Value |         | Description |

|------|------|-------------|---------|-------------|

| 31:0 | RW   | 0x0000000   | txdata2 |             |

### I2C\_TXDATA3

Address: Operational Base + offset (0x010c)

I2C transmit data register 3

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RW   | 0x0000000   | txdata3     |

### I2C\_TXDATA4

Address: Operational Base + offset (0x0110)

I2C transmit data register 4

| Bit  | Attr | Reset Value | , ,     | Description |

|------|------|-------------|---------|-------------|

| 31:0 | RW   | 0x00000000  | txdata4 |             |

### I2C\_TXDATA5

Address: Operational Base + offset (0x0114)

I2C transmit data register 5

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RW   | 0x00000000  | txdata5     |

### I2C\_TXDATA6

Address: Operational Base + offset (0x0118)

I2C transmit data register 6

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RW   | 0x00000000  | txdata6     |

### I2C\_TXDATA7

Address: Operational Base + offset (0x011c)

I2C transmit data register 7

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RW   | 0x00000000  | txdata7     |

### I2C\_RXDATA0

Address: Operational Base + offset (0x0200)

I2C receive data register 0

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RO   | 0x00000000  | rxdata0     |

### I2C\_RXDATA1

Address: Operational Base + offset (0x0204)

I2C receive data register 1

| Bit  | Attr | Reset Value | <b>Description</b> |  |

|------|------|-------------|--------------------|--|

| 31:0 | RO   | 0x00000000  | rxdata1            |  |

### I2C\_RXDATA2

Address: Operational Base + offset (0x0208)

I2C receive data register 2

| Bit  | Attr | Reset Value | Description |  |

|------|------|-------------|-------------|--|

| 31:0 | RO   | 0x0000000   | rxdata2     |  |

# I2C\_RXDATA3

Address: Operational Base + offset (0x020c)

I2C receive data register 3

| Bit  | Attr | Reset Value |         | Description |

|------|------|-------------|---------|-------------|

| 31:0 | RO   | 0x00000000  | rxdata3 |             |

### I2C\_RXDATA4

Address: Operational Base + offset (0x0210)

I2C receive data register 4

| Bit  | Attr | Reset Value |         | Description |

|------|------|-------------|---------|-------------|

| 31:0 | RO   | 0x00000000  | rxdata4 |             |

### I2C\_RXDATA5

Address: Operational Base + offset (0x0214)

I2C receive data register 5

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RO   | 0x00000000  | rxdata5     |

# I2C\_RXDATA6

Address: Operational Base + offset (0x0218)

I2C receive data register 6

| Bit  | Attr | Reset Value | Description |  |

|------|------|-------------|-------------|--|

| 31:0 | RO   | 0x00000000  | rxdata6     |  |

### I2C\_RXDATA7

Address: Operational Base + offset (0x021c)

I2C receive data register 7

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:0 | RO   | 0x00000000  | rxdata7     |

# **52.5 Interface description**

Table 52-1 I2C Interface Description

| Module pin         | Direction | Pad name                                           | IOMUX                           |  |  |

|--------------------|-----------|----------------------------------------------------|---------------------------------|--|--|

| I2C PMU Interface  |           |                                                    |                                 |  |  |

| i2c_pmu_sda        | I/O       | IO_I2C0PMUsda_P<br>MUgpio0b7                       | GRF_GPIO0B_IOMUX[1 4]=1         |  |  |

| i2c_pmu_scl        | I/O       | IO_I2C0PMUscl_P<br>MUgpio0c0                       | GRF_GPIOOC_IOMUX[0]=1           |  |  |

|                    | I2C       | SENSOR Interface                                   |                                 |  |  |

| i2c_sensor_sda     | I/O       | IO_I2C1SENSORsd<br>a_SCrst_GPIO1830<br>gpio8a4     | GRF_GPIO8A_IOMUX[9:8]=01        |  |  |

| i2c_sensor_scl     | I/O       | IO_I2C1SENSORsc<br>l_SCclk_GPIO1830<br>gpio8a5     | GRF_GPIO8A_IOMUX[1 1:10]=01     |  |  |

|                    | I20       | C AUDIO Interface                                  |                                 |  |  |

| i2c_audio_sda      | I/O       | IO_I2C2AUDIOsda<br>_AUDIOgpio6b1                   | GRF_GPIO6B_IOMUX[2<br>]=1       |  |  |

| i2c_audio_scl      | I/O       | IO_I2C2AUDIOscl_<br>AUDIOgpio6b2                   | GRF_GPIO6B_IOMUX[4]=1           |  |  |

| I2C CAM Interface  |           |                                                    |                                 |  |  |

| i2c_cam_sda        | I/O       | IO_I2C3CAMsda_D<br>VPgpio2c1                       | GRF_GPIO2C_IOMUX[2<br>]=1       |  |  |

| i2c_cam_scl        | I/O       | IO_I2C3CAMscl_D<br>VPgpio2c0                       | GRF_GPIO2C_IOMUX[0]=1           |  |  |

| I2C TP Interface   |           |                                                    |                                 |  |  |

| i2c_tp_sda         | I/O       | IO_I2C4TPsda_GPI<br>O30gpio7c1                     | GRF_GPIO7CL_IOMUX[<br>4]=1      |  |  |

| i2c_tp_scl         | I/O       | IO_I2C4TPscl_GPI<br>O30gpio7c2                     | GRF_GPIO7CL_IOMUX[<br>8]=1      |  |  |

| I2C HDMI Interface |           |                                                    |                                 |  |  |

| i2c_hdmi_sda       | I/O       | IO_I2C5HDMIsda_<br>EDPHDMII2Csda_G<br>PIO30gpio7c3 | GRF_GPIO7CL_IOMUX[<br>13:12]=01 |  |  |

| i2c_hdmi_scl I/O   |           | IO_I2C5HDMIscl_E<br>DPHDMII2Cscl_GPI<br>O30gpio7c4 | GRF_GPIO7CH_IOMUX<br>[1:0]=01   |  |  |

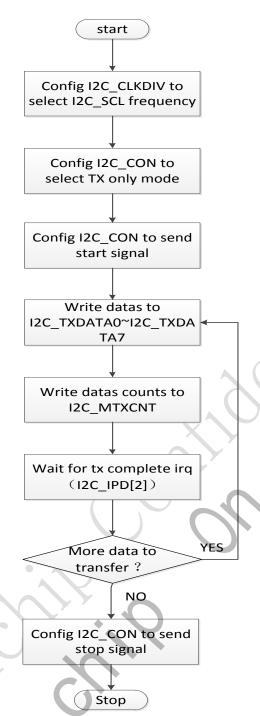

52.6 Ap plicatio n Notes

The I2C controller core operation flow chart below is to describe how the software configures and performs an I2C transaction through this I2C controller core. Description s are divided into 3 sections, transmit only mode, receive only mode,

and mix mode. Users are strongly advised to following.

Transmit only mode (I2C\_CON[1:0]=2′b00)

Fig. 52-6 I2C Flow chat for transmit only mode

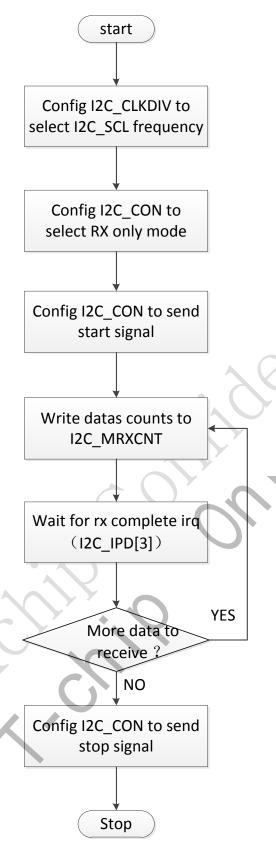

Receive only mode (I2C\_CON[1:0]=2'b10)

Fig. 52-7 I2C Flow chat for receive only mode

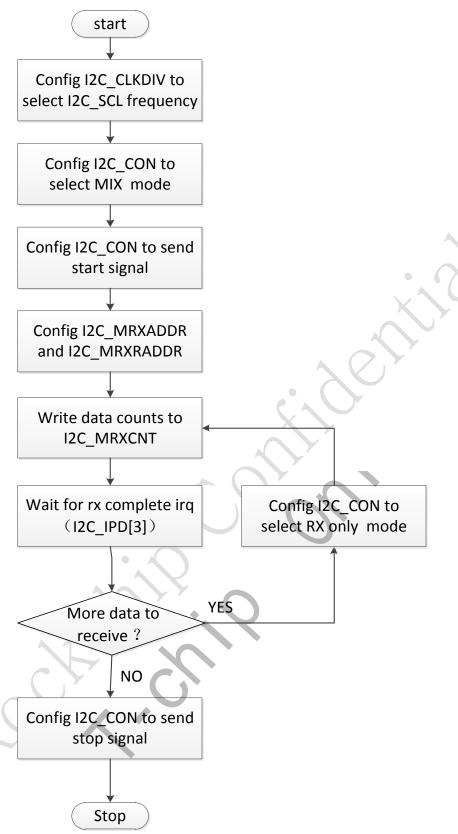

Mix mode (I2C\_CON[1:0]=2'b01 or I2C\_CON[1:0]=2'b11)

Fig. 52-8 I2C Flow chat for mix mode