# **Chapter 53 Universal Asynchronous Receiver/Transmitter**

# (UART)

# 53.1 Overview

The Universal Asynchronous Receiver/Transmitter (UART) is used for serial communication with a peripheral, modem (data carrier equipment, DCE) or data set. Data is written from a master (CPU) over the APB bus to the UART and it is converted to serial form and transmitted to the destination device. Serial data is also received by the UART and stored for the master (CPU) to read back.

UART Controller supports the following features:

- AMBA APB interface Allows for easy integration into a Synthesizable Components for AMBA 2 implementation

- Support interrupt interface to interrupt controller

- Contain two 64Bytes FIFOs for data receive and transmit

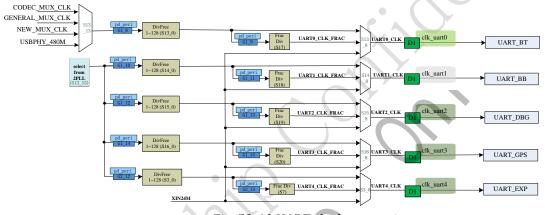

- Programmable serial data baud rate as calculated by the following: baud rate = (serial clock frequency)/(16×divisor)

- UART\_BB/UART\_BT/UART\_GPS/UART\_EXP support auto flow-control, UART\_DBG do not support auto flow-control

- UART\_DBG support IrDA 1.0 SIR mode with up to 115.2 Kbaud data rate

- UART\_BB/UART\_BT/UART\_GPS/UART\_EXP are in peripheral subsystem, UART\_DBG is in bus subsystem

# 53.2 Block Diagram

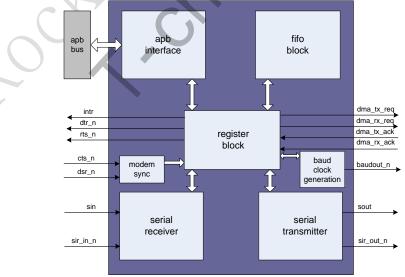

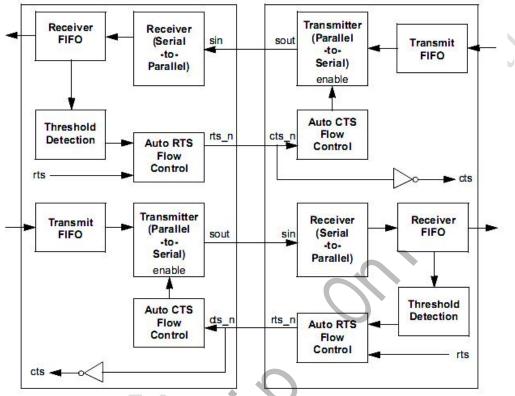

This section provides a description about the functions and behavior under various conditions. The UART Controller comprises with:

- AMBA APB interface

- FIFO controllers

- Register block

- Modem synchronization block and baud clock generation block

- Serial receiver and serial transmitter

Fig. 53-1 UART Architecture

## APB INTERFACE

The host processor accesses data, control, and status information on the UART through the APB interface. The UART supports APB data bus widths of 8, 16, and 32 bits.

### **Register block**

Be responsible for the main UART functionality including control, status and interrupt generation.

### **Modem Synchronization block**

Synchronizes the modem input signal.

### **FIFO block**

Be responsible for FIFO control and storage (when using internal RAM) or signaling to control external RAM (when used).

#### **Baud Clock Generator**

Generate the transmitter and receiver baud clock along with the output reference clock signal (baudout\_n).

#### **Serial Transmitter**

Converts the parallel data, written to the UART, into serial form and adds all additional bits, as specified by the control register, for transmission. This makeup of serial data, referred to as a character can exit the block in two forms, either serial UART format or IrDA 1.0 SIR format.

#### Serial Receiver

Converts the serial data character (as specified by the control register) received in either the UART or IrDA 1.0 SIR format to parallel form. Parity error detection, framing error detection and line break detection is carried out in this block.

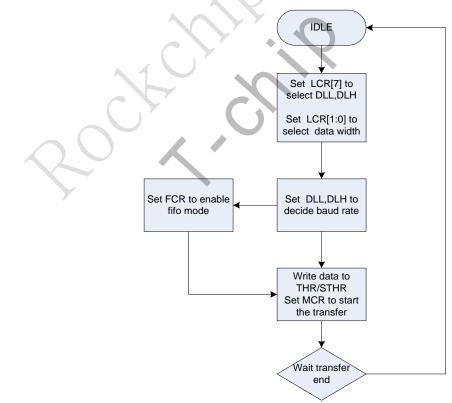

## **53.3 Function description**

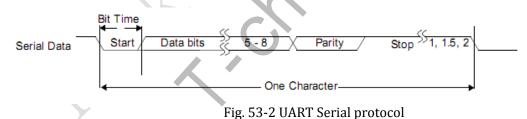

#### UART (RS232) Serial Protocol

Because the serial communication is asynchronous, additional bits (start and stop) are added to the serial data to indicate the beginning and end. An additional parity bit may be added to the serial character. This bit appears after the last data bit and before the stop bit(s) in the character structure to perform simple error checking on the received data, as shown in Figure.

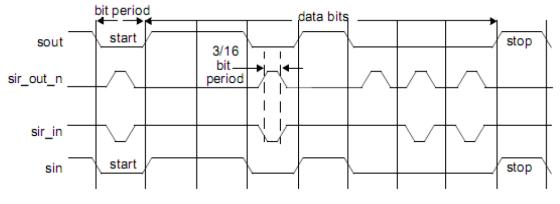

#### IrDA 1.0 SIR Protocol

The Infrared Data Association (IrDA) 1.0 Serial Infrared (SIR) mode supports bi-directional data communications with remote devices using infrared radiation as the transmission medium. IrDA 1.0 SIR mode specifies a maximum baud rate of 115.2 Kbaud.

Transmitting a single infrared pulse signals a logic zero, while a logic one is represented by not sending a pulse. The width of each pulse is 3/16ths of a normal serial bit time. Data transfers can only occur in half-duplex fashion when IrDA SIR mode is enabled.

Fig. 53-3 IrDA 1.0

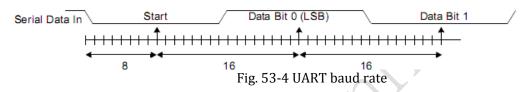

## **Baud Clock**

The baud rate is controlled by the serial clock (sclk or pclk in a single clock implementation) and the Divisor Latch Register (DLH and DLL). As the exact number of baud clocks that each bit was transmitted for is known, calculating the mid-point for sampling is not difficult, that is every 16 baud clocks after the mid point sample of the start bit.

### **FIFO Support**

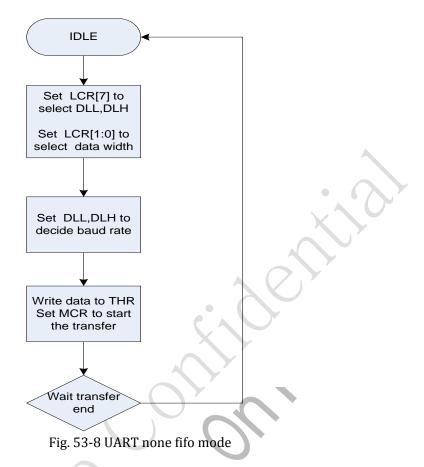

## **1. NONE FIFO MODE**

If FIFO support is not selected, then no FIFOs are implemented and only a single receive data byte and transmit data byte can be stored at a time in the RBR and THR.

## 2. FIFO MODE

The FIFO depth of UART1/UART2/UART3 is 32bytes and the FIFO depth of UART0 is 64bytes. The FIFO mode of all the UART is enabled by register FCR[0].

## Interrupts

The following interrupt types can be enabled with the IER register.

- Receiver Error

- Receiver Data Available

- Character Timeout (in FIFO mode only)

- Transmitter Holding Register Empty at/below threshold (in Programmable THRE Interrupt mode)

- Modem Status

## **DMA Support**

The uart supports DMA signaling with the use of two output signals (dma\_tx\_req\_n and dma\_rx\_req\_n) to indicate when data is ready to be read or when the transmit FIFO is empty.

The dma\_tx\_req\_n signal is asserted under the following conditions:

- When the Transmitter Holding Register is empty in non-FIFO mode.

- When the transmitter FIFO is empty in FIFO mode with Programmable THRE interrupt mode disabled.

- When the transmitter FIFO is at, or below the programmed threshold with Programmable THRE interrupt mode enabled.

The dma\_rx\_req\_n signal is asserted under the following conditions:

- When there is a single character available in the Receive Buffer Register in non-FIFO mode.

- When the Receiver FIFO is at or above the programmed trigger level in FIFO mode.

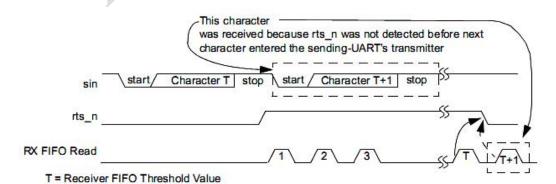

### **Auto Flow Control**

The UART can be configured to have a 16750-compatible Auto RTS and Auto CTS serial data flow control mode available. If FIFOs are not implemented, then this mode cannot be selected. When Auto Flow Control mode has been selected, it can be enabled with the Modem Control Register (MCR[5]). Following figure shows a block diagram of the Auto Flow Control functionality.

Fig. 53-5 UART Auto flow control block diagram

Auto RTS – Becomes active when the following occurs:

- Auto Flow Control is selected during configuration

- FIFOs are implemented

- RTS (MCR[1] bit and MCR[5]bit are both set)

- FIFOs are enabled (FCR[0]) bit is set)

- SIR mode is disabled (MCR[6] bit is not set)

Fig. 53-6 UART AUTO RTS TIMING

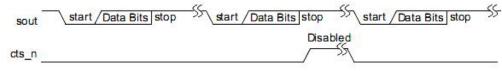

Auto CTS – becomes active when the following occurs:

- Auto Flow Control is selected during configuration

- FIFOs are implemented

- AFCE (MCR[5] bit is set)

- FIFOs are enabled through FIFO Control Register FCR[0] bit

- SIR mode is disabled (MCR[6] bit is not set)

Fig. 53-7 UART AUTO CTS TIMING

# **53.4 Register Description**

This section describes the control/status registers of the design. There are 5 UARTs in RK3288, and each one has its own base address.

## 53.4.1 Registers Summary

| Name       | Offset            | Size | <b>Reset Value</b> | Description                          |

|------------|-------------------|------|--------------------|--------------------------------------|

| UART_RBR   | 0x0000            | W    | 0x00000000         | Receive Buffer Register              |

| UART_THR   | 0x0000            | W    | 0x00000000         | Transmit Holding Register            |

| UART_DLL   | 0x0000            | W    | 0x00000000         | Divisor Latch (Low)                  |

| UART_DLH   | 0x0004            | W    | 0x00000000         | Divisor Latch (High)                 |

| UART_IER   | 0x0004            | W    | 0x00000000         | Interrupt Enable Register            |

| UART_IIR   | 0x0008            | W    | 0×0000001          | Interrupt Identification<br>Register |

| UART_FCR   | 0x0008            | W    | 0x00000000         | FIFO Control Register                |

| UART_LCR   | 0x000c            | W    | 0x00000000         | Line Control Register                |

| UART_MCR   | 0x0010            | W    | 0x00000000         | Modem Control Register               |

| UART_LSR   | 0x0014            | W    | 0x0000060          | Line Status Register                 |

| UART_MSR   | 0x0018            | W    | 0x00000000         | Modem Status Register                |

| UART_SCR   | 0x001c            | W    | 0x00000000         | Scratchpad Register                  |

| UART_SRBR  | 0x0030~<br>0x006c | w    | 0×00000000         | Shadow Receive Buffer<br>Register    |

| UART_STHR  | 0x0030~<br>0x006c | w    | 0x00000000         | Shadow Transmit Holding<br>Register  |

| UART_FAR   | 0x0070            | W    | 0x00000000         | FIFO Access Register                 |

| UART_TFR   | 0x0074            | W    | 0x00000000         | Transmit FIFO Read                   |

| UART_RFW   | 0x0078            | W    | 0x00000000         | Receive FIFO Write                   |

| UART_USR   | 0x007c            | W    | 0x0000006          | UART Status Register                 |

| UART_TFL   | 0x0080            | W    | 0x00000000         | Transmit FIFO Level                  |

| UART_RFL   | 0x0084            | W    | 0x00000000         | Receive FIFO Level                   |

| UART_SRR   | 0x0088            | W    | 0x0000000          | Software Reset Register              |

| UART_SRTS  | 0x008c            | W    | 0x0000000          | Shadow Request to Send               |

| UART_SBCR  | 0x0090            | W    | 0×00000000         | Shadow Break Control<br>Register     |

| UART_SDMAM | 0x0094            | W    | 0×00000000         | Shadow DMA Mode                      |

FuZhou Rockchip Electronics Co., Ltd.

| Name       | Offset   | Size | <b>Reset Value</b> | Description              |

|------------|----------|------|--------------------|--------------------------|

| UART_SFE   | 0x0098   | W    | 0x00000000         | Shadow FIFO Enable       |

| UART_SRT   | 0x009c   | W    | 0x00000000         | Shadow RCVR Trigger      |

| UART_STET  | 0x00a0   | W    | 0x0000000          | Shadow TX Empty Trigger  |

| UART_HTX   | 0x00a4   | W    | 0x0000000          | Halt TX                  |

| UART_DMASA | 0x00a8   | W    | 0x0000000          | DMA Software Acknowledge |

|            | 0x00f4 V | w    | 0x00000000         | Component Parameter      |

| UART_CPR   |          |      |                    | Register                 |

| UART_UCV   | 0x00f8   | W    | 0x3330382a         | UART Component Version   |

| UART_CTR   | 0x00fc   | W    | 0x44570110         | Component Type Register  |

Notes: <u>Size</u>: **B** - Byte (8 bits) access, **HW** - Half WORD (16 bits) access, **W** -WORD (32 bits) access

## 53.4.2 Detail Register Description

### UART\_RBR

Address: Operational Base + offset (0x0000) Receive Buffer Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7:0  | RW   | 0×00        | data_input<br>Data byte received on the serial input port<br>(sin) in UART mode, or the serial infrared<br>input (sir_in) in infrared mode. The data in<br>this register is valid only if the Data Ready<br>(DR) bit in the Line Status Register (LCR) is<br>set.<br>If in non-FIFO mode (FIFO_MODE == NONE)<br>or FIFOs are disabled (FCR[0] set to zero), the<br>data in the RBR must be read before the next<br>data arrives, otherwise it is overwritten,<br>resulting in an over-run error.<br>If in FIFO mode (FIFO_MODE != NONE) and<br>FIFOs are enabled (FCR[0] set to one), this<br>register accesses the head of the receive<br>FIFO. If the receive FIFO is full and this<br>register is not read before the next data<br>character arrives, then the data already in the<br>FIFO is preserved, but any incoming data are<br>lost and an over-run error occurs. |

### UART\_THR

Address: Operational Base + offset (0x0000) Transmit Holding Register

| Bit  | Attr | <b>Reset Value</b> | Description |

|------|------|--------------------|-------------|

| 31:8 | RO   | 0x0                | reserved    |

|             | data_output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 RW 0x00 | Data to be transmitted on the serial output<br>port (sout) in UART mode or the serial infrared<br>output (sir_out_n) in infrared mode. Data<br>should only be written to the THR when the<br>THR Empty (THRE) bit (LSR[5]) is set.<br>If in non-FIFO mode or FIFOs are disabled<br>(FCR[0] = 0) and THRE is set, writing a single<br>character to the THR clears the THRE. Any<br>additional writes to the THR before the THRE<br>is set again causes the THR data to be<br>overwritten.<br>If in FIFO mode and FIFOs are enabled<br>(FCR[0] = 1) and THRE is set, x number of<br>characters of data may be written to the THR<br>before the FIFO is full. The number x<br>(default=16) is determined by the value of<br>FIFO Depth that you set during configuration.<br>Any attempt to write data when the FIFO is full<br>results in the write data being lost. |

## UART\_DLL

Address: Operational Base + offset (0x0000)Divisor Latch (Low)

| Bit  | Attr  | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO    | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7:0  | CO, ≈ | 0×00        | baud_rate_divisor_L<br>Lower 8-bits of a 16-bit, read/write, Divisor<br>Latch register that contains the baud rate<br>divisor for the UART. This register may only be<br>accessed when the DLAB bit (LCR[7]) is set<br>and the UART is not busy (USR[0] is zero).<br>The output baud rate is equal to the serial<br>clock (sclk) frequency divided by sixteen<br>times the value of the baud rate divisor, as<br>follows: baud rate = (serial clock frequency) /<br>(16 * divisor).<br>Note that with the Divisor Latch Registers<br>(DLL and DLH) set to zero, the baud clock is<br>disabled and no serial communications occur.<br>Also, once the DLH is set, at least 8 clock<br>cycles of the slowest UART clock should be<br>allowed to pass before transmitting or<br>receiving data. |

## UART\_DLH

Address: Operational Base + offset (0x0004) Divisor Latch (High)

| Bit  | Attr | <b>Reset Value</b> | Description                                                                                                                                 |

|------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | 0x0                | reserved                                                                                                                                    |

| 7:0  | RW   | 0x00               | baud_rate_divisor_H<br>Upper 8 bits of a 16-bit, read/write, Divisor<br>Latch register that contains the baud rate<br>divisor for the UART. |

## UART\_IER

Address: Operational Base + offset (0x0004) Interrupt Enable Register

| Bit  | Attr | <b>Reset Value</b> | Description                                                                                                           |

|------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | 0x0                | reserved                                                                                                              |

|      |      |                    | prog_thre_int_en<br>Programmable THRE Interrupt Mode Enable                                                           |

| 7    | RW   | 0×0                | This is used to enable/disable the generation of THRE Interrupt.                                                      |

|      |      |                    | 1'b0: disabled                                                                                                        |

|      |      |                    | 1'b1: enabled                                                                                                         |

| 6:4  | RO   | 0x0                | reserved                                                                                                              |

|      |      |                    | modem_status_int_en<br>Enable Modem Status Interrupt.<br>This is used to enable/disable the generation                |

| 3    | RW   | 0x0                | of Modem Status Interrupt. This is the fourth<br>highest priority interrupt.<br>1'b0: disabled<br>1'b1: enabled       |

|      |      | FCY'               | receive_line_status_int_en<br>Enable Receiver Line Status Interrupt.<br>This is used to enable/disable the generation |

| 2    | RW   | 0×0                | of Receiver Line Status Interrupt. This is the<br>highest priority interrupt.<br>1'b0: disabled<br>1'b1: enabled      |

| 1    | RW   | 0×0                | trans_hold_empty_int_en<br>Enable Transmit Holding Register Empty<br>Interrupt.                                       |

| Bit | Attr | Reset Value | Description                                   |

|-----|------|-------------|-----------------------------------------------|

|     |      |             | receive_data_available_int_en                 |

|     |      |             | Enable Received Data Available Interrupt.     |

|     |      |             | This is used to enable/disable the generation |

|     |      |             | of Received Data Available Interrupt and the  |

| 0   | RW   | 0x0         | Character Timeout Interrupt (if in FIFO mode  |

|     |      |             | and FIFOs enabled). These are the second      |

|     |      |             | highest priority interrupts.                  |

|     |      |             | 1'b0: disabled                                |

|     |      |             | 1'b1: enabled                                 |

## UART\_IIR

Address: Operational Base + offset (0x0008) Interrupt Identification Register

| Bit    | Attr | Reset Value | Description                                    |

|--------|------|-------------|------------------------------------------------|

| 31:8   | RO   | 0x0         | reserved                                       |

|        |      |             | fifos_en                                       |

|        |      |             | FIFOs Enabled.                                 |

| 7:6    | RO   | 0x0         | This is used to indicate whether the FIFOs are |

| /.0    | κυ   | 0.00        | enabled or disabled.                           |

|        |      |             | 2'b00: disabled                                |

|        |      |             | 2'b11: enabled                                 |

| 5:4    | RO   | 0x0         | reserved                                       |

|        |      |             | int_id                                         |

|        |      |             | Interrupt ID                                   |

|        |      |             | This indicates the highest priority pending    |

|        |      |             | interrupt which can be one of the following    |

|        |      |             | types:                                         |

| 3:0    | RO   | 0x1         | 4'b0000: modem status                          |

| 5.0    |      |             | 4'b0001: no interrupt pending                  |

|        |      |             | 4'b0010: THR empty                             |

|        | C    | YC          | 4'b0100: received data available               |

| 0      |      |             | 4'b0110: receiver line status                  |

|        |      |             | 4'b0111: busy detect                           |

| $\sim$ |      |             | 4'b1100: character timeout                     |

|        | ·    |             |                                                |

## UART\_FCR

Address: Operational Base + offset (0x0008)

FIFO Control Register

| Bit  | Attr | <b>Reset Value</b> | Description |

|------|------|--------------------|-------------|

| 31:8 | RO   | 0x0                | reserved    |

| Bit               | Attr              | Reset Value               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Bit</b><br>7:6 | <b>Attr</b><br>WO | <b>Reset Value</b><br>0x0 | rcvr_trigger<br>RCVR Trigger.<br>This is used to select the trigger level in the<br>receiver FIFO at which the Received Data<br>Available Interrupt is generated. In auto flow<br>control mode it is used to determine when the<br>rts_n signal is de-asserted. It also determines<br>when the dma_rx_req_n signal is asserted in<br>certain modes of operation. The following<br>trigger levels are supported:<br>2'b00: 1 character in the FIFO<br>2'b01: FIFO 1/4 full<br>2'b10: FIFO 1/2 full |

| 5:4               | wo                | 0×0                       | 2'b11: FIFO 2 less than full<br>tx_empty_trigger<br>TX Empty Trigger.<br>This is used to select the empty threshold<br>level at which the THRE Interrupts are<br>generated when the mode is active. It also<br>determines when the dma_tx_req_n signal is<br>asserted when in certain modes of operation.<br>The following trigger levels are supported:<br>2'b00: FIFO empty<br>2'b01: 2 characters in the FIFO<br>2'b10: FIFO 1/4 full<br>2'b11: FIFO 1/2 full                                  |

| 3                 | wo                | 0×0                       | dma_mode<br>DMA Mode<br>This determines the DMA signalling mode<br>used for the dma_tx_req_n and<br>dma_rx_req_n output signals when additional<br>DMA handshaking signals are not selected .<br>1'b0: mode 0<br>1'b1: mode 11100 = character timeout.<br>xmit_fifo_reset<br>XMIT FIFO Reset.                                                                                                                                                                                                     |

| 2                 | wo                | 0×0                       | This resets the control portion of the transmit<br>FIFO and treats the FIFO as empty. This also<br>de-asserts the DMA TX request and single<br>signals when additional DMA handshaking<br>signals are select. Note that this bit is<br>'self-clearing'. It is not necessary to clear this<br>bit.                                                                                                                                                                                                 |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                               |

|-----|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | wo   | 0x0         | rcvr_fifo_reset<br>RCVR FIFO Reset.<br>This resets the control portion of the receive<br>FIFO and treats the FIFO as empty. This also<br>de-asserts the DMA RX request and single<br>signals when additional DMA handshaking<br>signals are selected. Note that this bit is<br>'self-clearing'. It is not necessary to clear this<br>bit. |

| 0   | wo   | 0×0         | fifo_en<br>FIFO Enable.<br>FIFO Enable. This enables/disables the<br>transmit (XMIT) and receive (RCVR) FIFOs.<br>Whenever the value of this bit is changed both<br>the XMIT and RCVR controller portion of FIFOs<br>is reset.                                                                                                            |

## UART\_LCR

Address: Operational Base + offset (0x000c) Line Control Register

| ontrol Re | gister |             |                                                   |

|-----------|--------|-------------|---------------------------------------------------|

| Bit       | Attr   | Reset Value | Description                                       |

| 31:8      | RO     | 0x0         | reserved                                          |

|           |        |             | div_lat_access                                    |

|           |        |             | Divisor Latch Access Bit.                         |

|           |        |             | Writeable only when UART is not busy              |

|           |        |             | (USR[0] is zero), always readable. This bit is    |

| 7         | RW     | 0x0         | used to enable reading and writing of the         |

|           |        | CY          | Divisor Latch register (DLL and DLH) to set the   |

|           |        |             | baud rate of the UART. This bit must be           |

|           |        |             | cleared after initial baud rate setup in order to |

|           | C      | Y C         | access other registers.                           |

|           |        |             | break_ctrl                                        |

|           |        |             | Break Control Bit.                                |

|           |        |             | This is used to cause a break condition to be     |

|           |        |             | transmitted to the receiving device. If set to    |

| Ť         |        |             | one the serial output is forced to the spacing    |

|           |        |             | (logic 0) state. When not in Loopback Mode,       |

| 6         | RW     | 0x0         | as determined by MCR[4], the sout line is         |

|           |        |             | forced low until the Break bit is cleared. If     |

|           |        |             | MCR[6] set to one, the sir_out_n line is          |

|           |        |             | continuously pulsed. When in Loopback Mode,       |

|           |        |             | the break condition is internally looped back     |

|           |        |             | to the receiver and the sir_out_n line is forced  |

|           |        |             | low.                                              |

| 5         | RO     | 0x0         | reserved                                          |

| Bit | Attr | Reset Value | Description                                      |

|-----|------|-------------|--------------------------------------------------|

|     |      |             | even_parity_sel                                  |

|     |      |             | Even Parity Select.                              |

|     |      |             | Writeable only when UART is not busy             |

|     |      |             | (USR[0] is zero), always readable. This is       |

| 4   | RW   | 0x0         | used to select between even and odd parity,      |

|     |      |             | when parity is enabled (PEN set to one). If set  |

|     |      |             | to one, an even number of logic 1s is            |

|     |      |             | transmitted or checked. If set to zero, an odd   |

|     |      |             | number of logic 1s is transmitted or checked.    |

|     |      |             | parity_en                                        |

|     |      |             | Parity Enable.                                   |

|     |      |             | Writeable only when UART is not busy             |

|     |      |             | (USR[0] is zero), always readable. This bit is   |

| 3   | RW   | 0x0         | used to enable and disable parity generation     |

|     |      |             | and detection in transmitted and received        |

|     |      |             | serial character respectively.                   |

|     |      |             | 1'b0: parity disabled                            |

|     |      |             | 1'b1: parity enabled                             |

|     |      |             | stop_bits_num                                    |

|     |      |             | Number of stop bits.                             |

|     |      |             | Writeable only when UART is not busy             |

|     |      |             | (USR[0] is zero), always readable. This is       |

|     |      |             | used to select the number of stop bits per       |

|     |      |             | character that the peripheral transmits and      |

|     |      |             | receives. If set to zero, one stop bit is        |

|     |      | •           | transmitted in the serial data.If set to one and |

| 2   | RW   | 0x0         | the data bits are set to 5 (LCR[1:0] set to      |

|     |      |             | zero) one and a half stop bits is transmitted.   |

|     |      |             | Otherwise, twostop bits are transmitted. Note    |

|     |      |             | that regardless of the number of stop bits       |

|     |      |             | select, the receiver checks only the first stop  |

|     | L    |             | bit.                                             |

|     |      | 11          | 1'b0: 1 stop bit                                 |

|     |      |             | 1'b1: 1.5 stop bits when DLS (LCR[1:0]) is       |

|     |      |             | zero, else 2 stop bit.                           |

| Bit | Attr | <b>Reset Value</b> | Description                                                                                                                                                                                                                                                                                                                                                         |

|-----|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | RW   | 0×0                | data_length_sel<br>Data Length Select.<br>Writeable only when UART is not busy<br>(USR[0] is zero), always readable. This is<br>used to select the number of data bits per<br>character that the peripheral transmits and<br>receives. The number of bit that may be<br>selected areas follows:<br>2'b00: 5 bits<br>1'b01: 6 bits<br>1'b10: 7 bits<br>1'b11: 8 bits |

### UART\_MCR

Address: Operational Base + offset (0x0010) Modem Control Register

| MCR<br>s: Operational Base + offset (0x0010)<br>Control Register |                        |                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Attr                                                             | <b>Reset Value</b>     | Description                                                                                                                                                                                                                                                                                                          |  |  |

| RO                                                               | 0x0                    | reserved                                                                                                                                                                                                                                                                                                             |  |  |

|                                                                  |                        | sir_mode_en                                                                                                                                                                                                                                                                                                          |  |  |

|                                                                  |                        | SIR Mode Enable.                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                  |                        | SIR Mode Enable.                                                                                                                                                                                                                                                                                                     |  |  |

| RW                                                               | 0x0                    | This is used to enable/disable the IrDA SIR                                                                                                                                                                                                                                                                          |  |  |

|                                                                  |                        | Mode.                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                  |                        | 1'b0: IrDA SIR Mode disabled                                                                                                                                                                                                                                                                                         |  |  |

|                                                                  |                        | 1'b1: IrDA SIR Mode enabled                                                                                                                                                                                                                                                                                          |  |  |

|                                                                  | 0x0                    | auto_flow_ctrl_en                                                                                                                                                                                                                                                                                                    |  |  |

| ۵ <b>۱</b> ۸/                                                    |                        | Auto Flow Control Enable.                                                                                                                                                                                                                                                                                            |  |  |

|                                                                  |                        | 1'b0: Auto Flow Control Mode disabled                                                                                                                                                                                                                                                                                |  |  |

| A.                                                               |                        | 1'b1: Auto Flow Control Mode enabled                                                                                                                                                                                                                                                                                 |  |  |

|                                                                  | 0×0                    | loopback                                                                                                                                                                                                                                                                                                             |  |  |

| RW                                                               |                        | LoopBack Bit.                                                                                                                                                                                                                                                                                                        |  |  |

|                                                                  |                        | This is used to put the UART into a diagnostic                                                                                                                                                                                                                                                                       |  |  |

|                                                                  |                        | mode for test purposes.                                                                                                                                                                                                                                                                                              |  |  |

|                                                                  |                        | out2                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                  |                        | OUT2.                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                  |                        | This is used to directly control the                                                                                                                                                                                                                                                                                 |  |  |

| >\\/                                                             | 0x0                    | user-designated Output2 (out2_n) output.                                                                                                                                                                                                                                                                             |  |  |

|                                                                  |                        | The value written to this location is inverted                                                                                                                                                                                                                                                                       |  |  |

|                                                                  |                        | and driven out on out2_n, that is:                                                                                                                                                                                                                                                                                   |  |  |

|                                                                  |                        | 1'b0: out2_n de-asserted (logic 1)                                                                                                                                                                                                                                                                                   |  |  |

|                                                                  |                        | 1'b1: out2_n asserted (logic 0)                                                                                                                                                                                                                                                                                      |  |  |

| 2\\/                                                             | 0×0                    | out1                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                  |                        | OUT1                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                  | Attr<br>Attr<br>O<br>W | Attr Reset Value   Image: Color of the set value 0x0   Image: Color of the value 0x0 |  |  |

| Bit  | Attr                                                   | Reset Value | Description                                     |  |

|------|--------------------------------------------------------|-------------|-------------------------------------------------|--|

|      |                                                        |             | req_to_send                                     |  |

|      |                                                        |             | Request to Send.                                |  |

|      |                                                        |             | This is used to directly control the Request to |  |

| 1    | RW                                                     | 0x0         | Send (rts_n) output. The Request To Send        |  |

|      |                                                        |             | (rts_n) output is used to inform the modem or   |  |

|      |                                                        |             | data set that the UART is ready to exchange     |  |

|      |                                                        |             | data.                                           |  |

|      |                                                        |             | data_terminal_ready                             |  |

|      | RW                                                     | 0x0         | Data Terminal Ready.                            |  |

|      |                                                        |             | This is used to directly control the Data       |  |

| 0    |                                                        |             | Terminal Ready (dtr_n) output. The value        |  |

| 0    | RW                                                     | UXU         | written to this location is inverted and driven |  |

|      |                                                        |             | out on dtr_n, that is:                          |  |

|      |                                                        |             | 1'b0: dtr_n de-asserted (logic 1)               |  |

|      |                                                        |             | 1'b1: dtr_n asserted (logic 0)                  |  |

|      |                                                        |             |                                                 |  |

| _LSR |                                                        |             |                                                 |  |

|      | s: Operational Base + offset (0x0014)<br>atus Register |             |                                                 |  |

## UART\_LSR

Address: Operational Base + offset (0x0014)Line Status Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                      |

|------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                         |

| 7    | RO   | 0×0         | receiver_fifo_error<br>Receiver FIFO Error bit.<br>This bit is relevant FIFOs are enabled (FCR[0]<br>set to one). This is used to indicate if there is<br>at least one parity error, framing error, or<br>break indication in the FIFO.<br>1'b0: no error in RX FIFO<br>1'b1: error in RX FIFO                                                   |

| 6    | RO   | 0×1         | trans_empty<br>Transmitter Empty bit.<br>Transmitter Empty bit. If FIFOs enabled<br>(FCR[0] set to one), this bit is set whenever<br>the Transmitter Shift Register and the FIFO<br>are both empty. If FIFOs are disabled, this bit<br>is set whenever the Transmitter Holding<br>Register and the Transmitter Shift Register<br>are both empty. |

| Bit | Attr | Reset Value | Description                                       |

|-----|------|-------------|---------------------------------------------------|

|     |      |             | trans_hold_reg_empty                              |

|     |      |             | Transmit Holding Register Empty bit.              |

|     |      |             | If THRE mode is disabled (IER[7] set to zero)     |

|     |      |             | and regardless of FIFO's being                    |

|     |      |             | implemented/enabled or not, this bit indicates    |

|     |      |             | that the THR or TX FIFO is empty.                 |

|     |      |             | This bit is set whenever data is transferred      |

|     |      |             | from the THR or TX FIFO to the transmitter        |

| 5   | RO   | 0x1         | shift register and no new data has been           |

|     |      |             | written to the THR or TX FIFO. This also          |

|     |      |             | causes a THRE Interrupt to occur, if the THRE     |

|     |      |             | Interrupt is enabled. If IER[7] set to one and    |

|     |      |             | FCR[0] set to one respectively, the               |

|     |      |             | functionality is switched to indicate the         |

|     |      |             | transmitter FIFO is full, and no longer controls  |

|     |      |             | THRE interrupts, which are then controlled by     |

|     |      |             | the FCR[5:4] threshold setting.                   |

|     |      |             | break_int                                         |

|     |      |             | Break Interrupt bit.                              |

| 4   | RO   | 0x0         | This is used to indicate the detection of a       |

|     |      |             | break sequence on the serial input data.          |

|     |      |             | framing_error                                     |

|     |      |             | Framing Error bit.                                |

| 2   |      | 00          | This is used to indicate the occurrence of a      |

| 3   | RO   | 0x0         | framing error in the receiver. A framing error    |

|     |      | •           | occurs when the receiver does not detect a        |

|     |      |             | valid STOP bit in the received data.              |

|     |      |             | parity_eror                                       |

|     |      |             | Parity Error bit.                                 |

| 2   | RO   | 0x0         | This is used to indicate the occurrence of a      |

|     |      |             | parity error in the receiver if the Parity Enable |

|     |      |             | (PEN) bit (LCR[3]) is set.                        |

|     |      | 11          | overrun_error                                     |

|     |      |             | Overrun error bit.                                |

| 1   | RO   | 0x0         | This is used to indicate the occurrence of an     |

| -   |      |             | overrun error. This occurs if a new data          |

|     |      |             | character was received before the previous        |

|     |      |             | data was read.                                    |

|     |      |             | data_ready                                        |

|     |      |             | Data Ready bit.                                   |

|     |      |             | This is used to indicate that the receiver        |

| 0   | RO   | 0x0         | contains at least one character in the RBR or     |

|     |      |             | the receiver FIFO.                                |

|     |      |             | 1'b0: no data ready                               |

|     |      |             | 1'b1: data ready                                  |

## UART\_MSR

Address: Operational Base + offset (0x0018) Modem Status Register

| Bit  | Attr | <b>Reset Value</b> | Description                                       |

|------|------|--------------------|---------------------------------------------------|

| 31:8 | RO   | 0x0                | reserved                                          |

|      |      |                    | data_carrior_detect                               |

| 7    |      |                    | Data Carrier Detect.                              |

| 7    | RO   | 0x0                | This is used to indicate the current state of the |

|      |      |                    | modem control line dcd_n.                         |

|      |      |                    | ring_indicator                                    |

| C    |      |                    | Ring Indicator.                                   |

| 6    | RO   | 0x0                | This is used to indicate the current state of the |

|      |      |                    | modem control line ri_n.                          |

|      |      |                    | data_set_ready                                    |

| -    |      |                    | Data Set Ready.                                   |

| 5    | RO   | 0x0                | This is used to indicate the current state of the |

|      |      |                    | modem control line dsr_n.                         |

|      |      |                    | clear_to_send                                     |

|      |      | 00                 | Clear to Send.                                    |

| 4    | RO   | 0x0                | This is used to indicate the current state of the |

|      |      |                    | modem control line cts_n.                         |

|      |      |                    | delta_data_carrier_detect                         |

|      |      |                    | Delta Data Carrier Detect.                        |

| 3    | RO   | 0x0                | This is used to indicate that the modem           |

|      |      |                    | control line dcd_n has changed since the last     |

|      |      |                    | time the MSR was read.                            |

|      |      |                    | trailing_edge_ring_indicator                      |

|      |      |                    | Trailing Edge of Ring Indicator.                  |

|      |      | C Y                | Trailing Edge of Ring Indicator. This is used to  |

| 2    | RO   | 0x0                | indicate that a change on the input ri_n (from    |

|      |      |                    | an active-low to an inactive-high state) has      |

|      | C    | Y' C               | occurred since the last time the MSR was          |

|      |      |                    | read.                                             |

|      |      |                    | delta_data_set_ready                              |

|      |      |                    | Delta Data Set Ready.                             |

| 1    | RO   | 0x0                | This is used to indicate that the modem           |

|      |      |                    | control line dsr_n has changed since the last     |

|      |      |                    | time the MSR was read.                            |

|      |      |                    | delta_clear_to_send                               |

|      |      |                    | Delta Clear to Send.                              |

| 0    | RO   | 0x0                | This is used to indicate that the modem           |

|      |      |                    | control line cts_n has changed since the last     |

|      |      |                    | time the MSR was read.                            |

## **UART\_SCR** Address: Operational Base + offset (0x001c)

Scratchpad Register

| Bit  | Attr | Reset Value | Description                                  |

|------|------|-------------|----------------------------------------------|

| 31:8 | RO   | 0x0         | reserved                                     |

| 51.0 | κυ   |             |                                              |

|      |      |             | temp_store_space                             |

| 7:0  | RW   | 0x00        | This register is for programmers to use as a |

|      |      |             | temporary storage space.                     |

#### UART\_SRBR

Address: Operational Base + offset (0x0030~0x006c) Shadow Receive Buffer Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7:0  | RO   | 0×00        | shadow_rbr<br>This is a shadow register for the RBR and has<br>been allocated sixteen 32-bit locations so as<br>to accommodate burst accesses from the<br>master. This register contains the data byte<br>received on the serial input port (sin) in UART<br>mode or the serial infrared input (sir_in) in<br>infrared mode. The data in this register is valid<br>only if the Data Ready (DR) bit in the Line<br>status Register (LSR) is set.<br>If FIFOs are disabled (FCR[0] set to zero), the<br>data in the RBR must be read before the next<br>data arrives, otherwise it is overwritten,<br>resulting in an overrun error.<br>If FIFOs are enabled (FCR[0] set to one), this<br>register accesses the head of the receive<br>FIFO. If the receive FIFO is full and this<br>register is not read before the next data<br>character arrives, then the data already in the<br>FIFO are preserved, but any incoming data is<br>lost. An overrun error also occurs. |

## UART\_STHR

Address: Operational Base + offset (0x0030~0x006c) Shadow Transmit Holding Register

| Bit  | Attr | <b>Reset Value</b> | Description                                          |

|------|------|--------------------|------------------------------------------------------|

| 31:8 | RO   | 0x0                | reserved                                             |

| 7:0  | RO   | 0x00               | shadow_thr<br>This is a shadow register for the THR. |

## UART\_FAR

Address: Operational Base + offset (0x0070) FIFO Access Register

| Bit Attr | <b>Reset Value</b> | Description |

|----------|--------------------|-------------|

|----------|--------------------|-------------|

| Bit  | Attr | Reset Value | Description                                     |

|------|------|-------------|-------------------------------------------------|

| 31:1 | RO   | 0x0         | reserved                                        |

|      |      |             | fifo_access_test_en                             |

|      |      |             | This register is use to enable a FIFO access    |

|      |      |             | mode for testing, so that the receive FIFO can  |

|      |      |             | be written by the master and the transmit       |

|      |      |             | FIFO can be read by the master when FIFOs       |

| 0    | RW   | 0x0         | are implemented and enabled. When FIFOs         |

|      |      |             | are not enabled it allows the RBR to be written |

|      |      |             | by the master and the THR to be read by the     |

|      |      |             | master.                                         |

|      |      |             | 1'b0: FIFO access mode disabled                 |

|      |      |             | 1'b1: FIFO access mode enabled                  |

### UART\_TFR

Address: Operational Base + offset (0x0074) Transmit FIFO Read

| Bit  | Attr | Reset Value | Description                                     |

|------|------|-------------|-------------------------------------------------|

| 31:8 | RO   | 0x0         | reserved                                        |

|      |      |             | trans_fifo_read                                 |

|      |      |             | Transmit FIFO Read.                             |

|      |      |             | These bits are only valid when FIFO access      |

|      |      |             | mode is enabled (FAR[0] is set to one).When     |

| 7:0  | RO   | 0x00        | FIFOs are implemented and enabled, reading      |

|      |      |             | this register gives the data at the top of the  |

|      |      |             | transmit FIFO. Each consecutive read pops       |

|      |      |             | the transmit FIFO and gives the next data       |

|      |      |             | value that is currently at the top of the FIFO. |

## UART\_RFW

Address: Operational Base + offset (0x0078) Receive FIFO Write

| Bit   | Attr | Reset Value | Description                                |

|-------|------|-------------|--------------------------------------------|

| 31:10 | RO   | 0x0         | reserved                                   |

|       |      |             | receive_fifo_framing_error                 |

| 0     | wo   |             | Receive FIFO Framing Error.                |

| 9     | 9 WO | 0×0         | These bits are only valid when FIFO access |

|       |      |             | mode is enabled (FAR[0] is set to one).    |

|       |      |             | receive_fifo_parity_error                  |

| 0     | wo   | 0x0         | Receive FIFO Parity Error.                 |

| 8     | WO   |             | These bits are only valid when FIFO access |

|       |      |             | mode is enabled (FAR[0] is set to one).    |

| Bit | Attr   | Reset Value | Description                                                                                |

|-----|--------|-------------|--------------------------------------------------------------------------------------------|

|     |        |             | receive_fifo_write<br>Receive FIFO Write Data.                                             |

|     |        |             | These bits are only valid when FIFO access mode is enabled (FAR[0] is set to one). When    |

| 7:0 | 7:0 WO | 0x00        | FIFOs are enabled, the data that is written to the RFWD is pushed into the receive FIFO.   |

|     |        |             | Each consecutive write pushes the new data to the next write location in the receive FIFO. |

|     |        |             | When FIFOs not enabled, the data that is written to the RFWD is pushed into the RBR.       |

•

## UART\_USR

Address: Operational Base + offset (0x007c) UART Status Register

| Bit  | Attr       | Reset Value | Description                                       |

|------|------------|-------------|---------------------------------------------------|

| 31:5 | RO         | 0x0         | reserved                                          |

|      |            |             | receive_fifo_full                                 |

|      |            |             | Receive FIFO Full.                                |

|      |            |             | This is used to indicate that the receive FIFO is |

| 4    | RO         | 0x0         | completely full.                                  |

| -    |            | 0.00        | 1'b0: Receive FIFO not full                       |

|      |            |             | 1'b1: Receive FIFO Full                           |

|      |            |             | This bit is cleared when the RX FIFO is no        |

|      |            |             | longer full.                                      |

|      |            |             | receive_fifo_not_empty                            |

|      |            |             | Receive FIFO Not Empty.                           |

|      |            |             | This is used to indicate that the receive FIFO    |

| 3    | RO         | 0x0         | contains one or more entries.                     |

|      |            |             | 1'b0: Receive FIFO is empty                       |

|      |            |             | 1'b1: Receive FIFO is not empty                   |

|      |            | Y C         | This bit is cleared when the RX FIFO is empty.    |

|      |            |             | trasn_fifo_empty                                  |

|      | $\bigcirc$ |             | Transmit FIFO Empty.                              |

|      |            |             | This is used to indicate that the transmit FIFO   |

| 2    | RO         | 0x1         | is completely empty.                              |

|      |            |             | 1'b0: Transmit FIFO is not empty                  |

|      |            |             | 1'b1: Transmit FIFO is empty                      |

|      |            |             | This bit is cleared when the TX FIFO is no        |

|      |            |             | longer empty                                      |

| Bit | Attr | Reset Value | Description                                     |

|-----|------|-------------|-------------------------------------------------|

|     |      |             | trans_fifo_not_full                             |

|     |      |             | Transmit FIFO Not Full.                         |

|     |      |             | This is used to indicate that the transmit FIFO |

| 1   | RO   | 0x1         | in not full.                                    |

|     |      |             | 1'b0: Transmit FIFO is full                     |

|     |      |             | 1'b1: Transmit FIFO is not full                 |

|     |      |             | This bit is cleared when the TX FIFO is full.   |

|     |      |             | uart_busy                                       |

|     |      |             | UART Busy.                                      |

|     |      |             | UART Busy. This is indicates that a serial      |

| 0   | RO   | 0x0         | transfer is in progress, when cleared indicates |

|     |      |             | that the UART is idle or inactive.              |

|     |      |             | 1'b0: UART is idle or inactive                  |

|     |      |             | 1'b1: UART is busy (actively transferring data) |

## UART\_TFL

Address: Operational Base + offset (0x0080) Transmit FIFO Level

| Bit  | Attr   | <b>Reset Value</b> | Description                                     |

|------|--------|--------------------|-------------------------------------------------|

| 31:5 | RO     | 0x0                | reserved                                        |

|      | 4:0 RW | / 0x00             | trans_fifo_level                                |

| 4:0  |        |                    | Transmit FIFO Level.                            |

|      |        |                    | This is indicates the number of data entries in |

|      |        |                    | the transmit FIFO.                              |

## UART\_RFL

Address: Operational Base + offset (0x0084) Receive FIFO Level

| Bit  | Attr      | <b>Reset Value</b> | Description                                     |

|------|-----------|--------------------|-------------------------------------------------|

| 31:5 | RO        | 0x0                | reserved                                        |

|      |           | 0x00               | receive_fifo_level                              |

| 4:0  | RO        |                    | Receive FIFO Level.                             |

| 4.0  | RU        | 0,00               | This is indicates the number of data entries in |

|      | $\bigcap$ |                    | the receive FIFO.                               |

|      |           |                    |                                                 |

## UART\_SRR

Address: Operational Base + offset (0x0088) Software Reset Register

| Bit  | Attr | Reset Value | Description                                                                                               |

|------|------|-------------|-----------------------------------------------------------------------------------------------------------|