# PRODUCT DATA SHEET

# RK27XX

Revision A1.1 October, 2007

# TABLE OF CONTENT

| TABLE OF CONTENT                                              |    |

|---------------------------------------------------------------|----|

| About This Manual                                             |    |

| Release Note                                                  |    |

| Document Version Information                                  |    |

| Document History                                              | 9  |

| Chapter 1 Product Overview                                    |    |

| 1.1 Overview                                                  |    |

| Features                                                      |    |

| 1.3 Pin Diagram                                               |    |

| 1.4 Pin Description                                           |    |

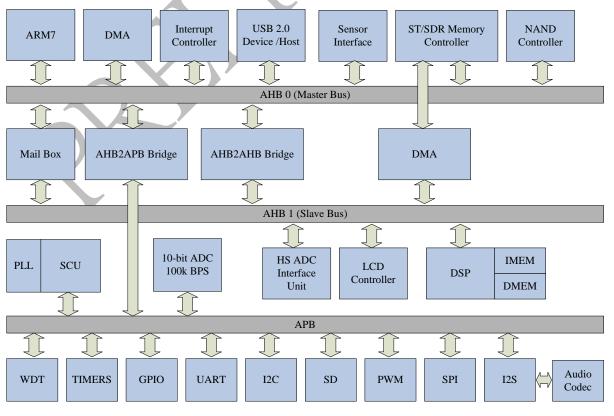

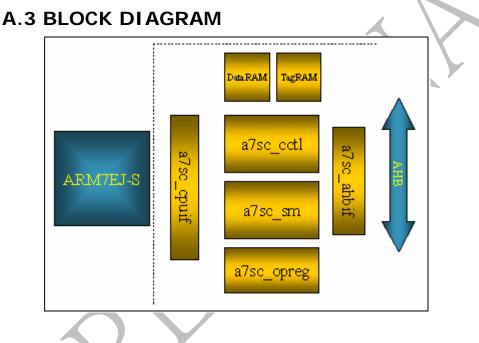

| 1.5 Architercture                                             | 17 |

| 1.5.1 Block Diagram.                                          | 1/ |

| Chapter 2 System Configuration                                |    |

| 2.1 Descriptions                                              |    |

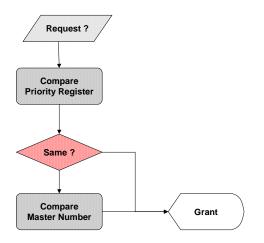

| 2.1.1 AHB Master Priority                                     | 10 |

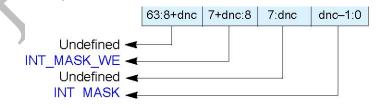

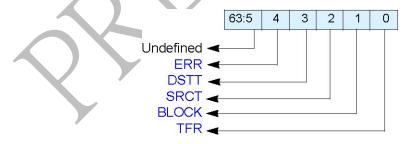

| 2.1.2 Interrupts                                              | 18 |

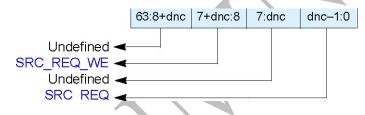

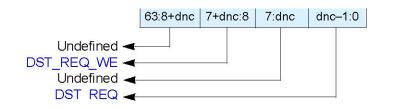

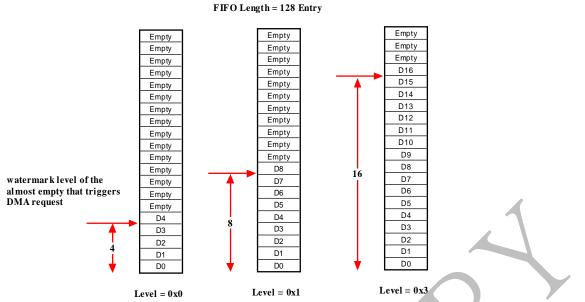

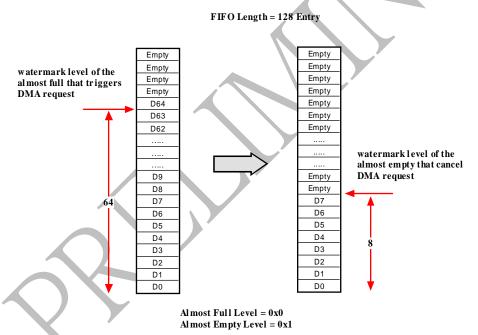

| 2.1.3 DMA hardware request                                    | 19 |

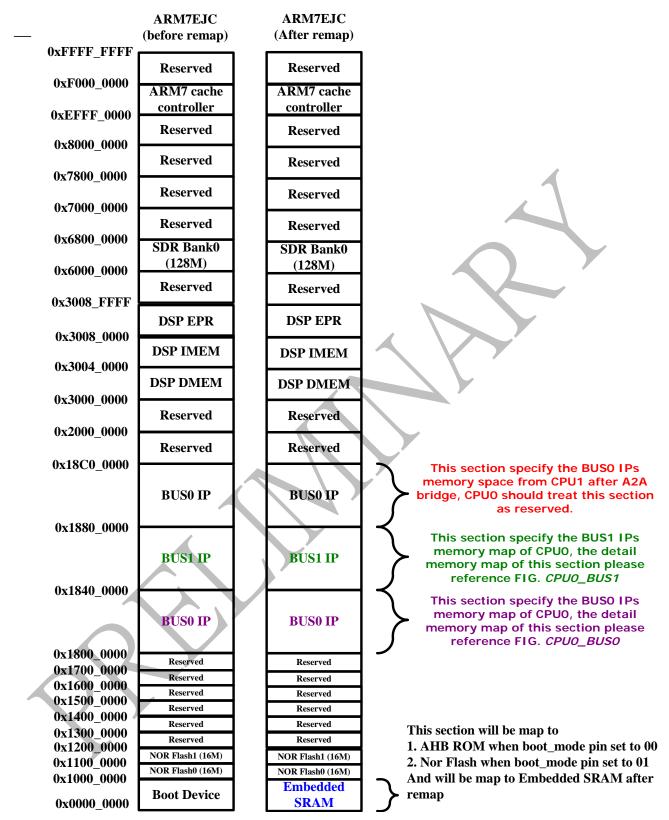

| 2.2 System Address Map                                        | 20 |

| 2.2.1 Default Memory Map<br>2.2.2 System Memory Map for ARM   | 20 |

| 2.2.2 System Memory Map for ARM                               | 21 |

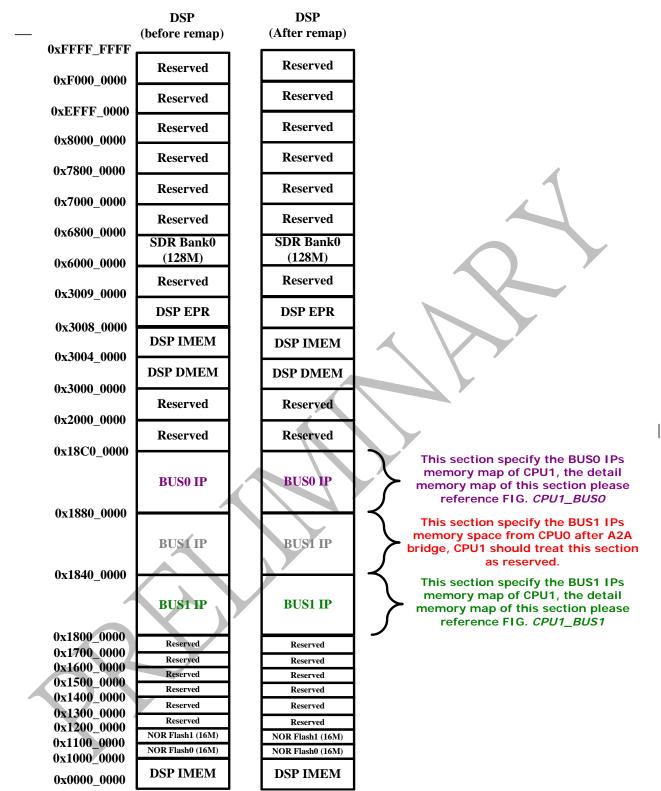

| 2.2.3 System Memory Map for DSP                               | 24 |

| 2.3 System mode configuration                                 | 27 |

| 2.3.1 Debug mode                                              | 27 |

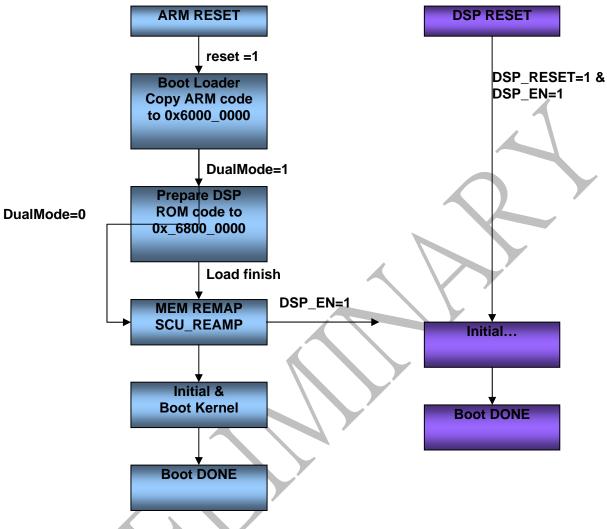

| 2.3.2 CPU Boot mode<br>Chapter 3 Dual-Core Communication Unit | 2/ |

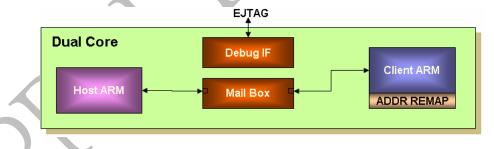

| Chapter 3 Dual-Core Communication Unit                        | 28 |

| 3.1 Design Overview                                           | 28 |

| 3.1.1 Overview                                                | 28 |

| 3.1.2 Features                                                | 28 |

| 3.2 Architecture                                              |    |

| 3.2.1 Block Diagram                                           |    |

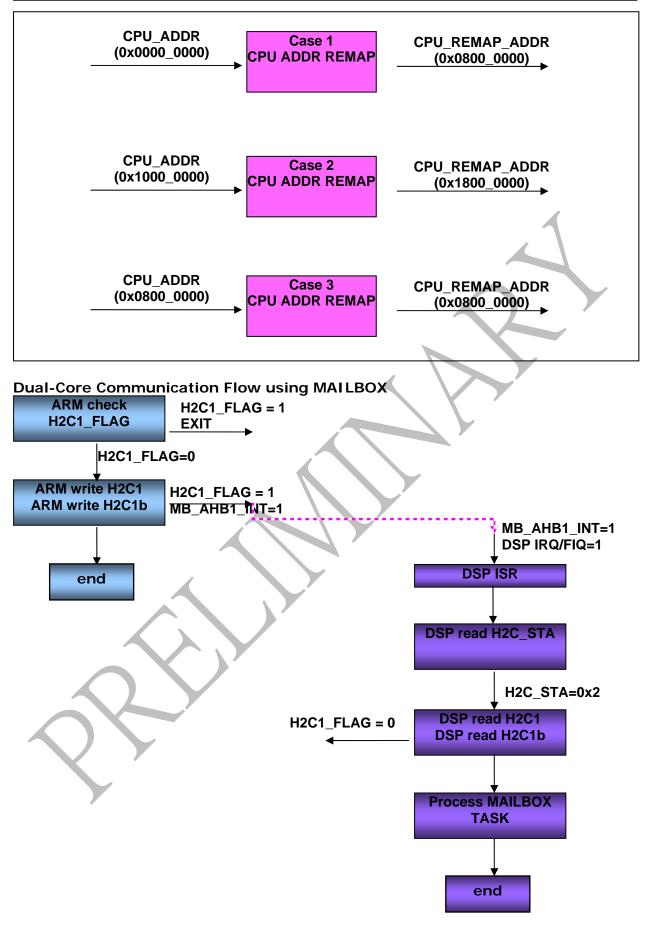

| 3.2.2 CPU_ADDR_REMAP Descriptions                             |    |

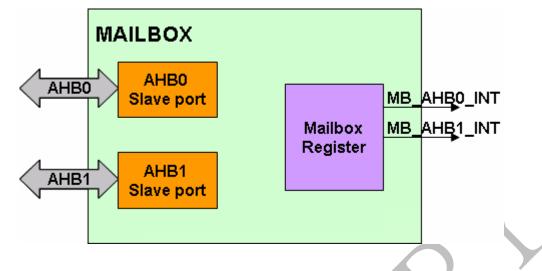

| 3.2.3 MAILBOX Block Diagram                                   |    |

| 3.2.4 MAILBOX Block Descriptions                              |    |

| 3.3 Registers                                                 |    |

| 3.3.1 MAILBOX Registers Summary                               | 29 |

| 3.3.2 MAILBOX Detail Register Description                     |    |

| 3.4 Function Description                                      |    |

|                                                               |    |

| 3.4.2 Programming sequence                                    |    |

| Chapter 4 AHB Bus Arbiter                                     |    |

|                                                               |    |

| 4.1.1 Overview                                                |    |

| 4.1.2 Features                                                |    |

| 4.2 Registers                                                 |    |

| 4.2.1 Registers Summary                                       |    |

| 4.2.2 Detail Register Description                             |    |

| 4.3 Functional Description                                    |    |

| 4.3.1 Operation                                               |    |

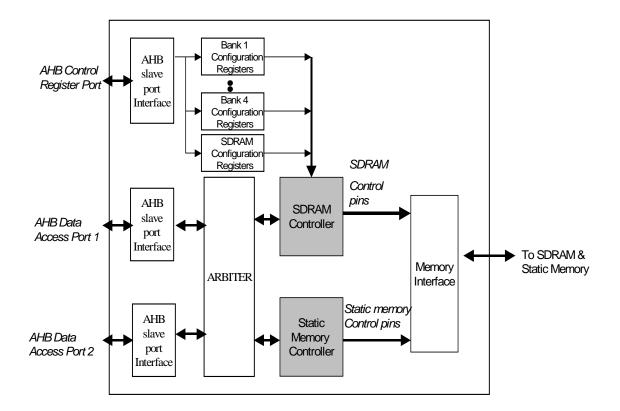

| Chapter 5 Static/SDRAM Memory Controller                      |    |

| 5.1 Design Overview                                           |    |

|                                                               |    |

|                                                               |    |

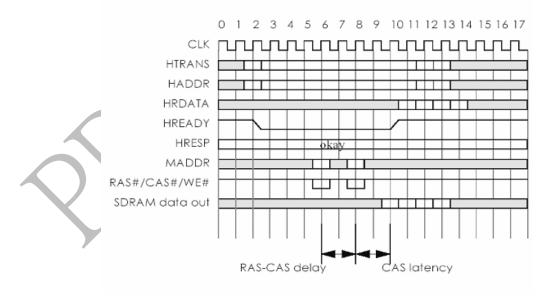

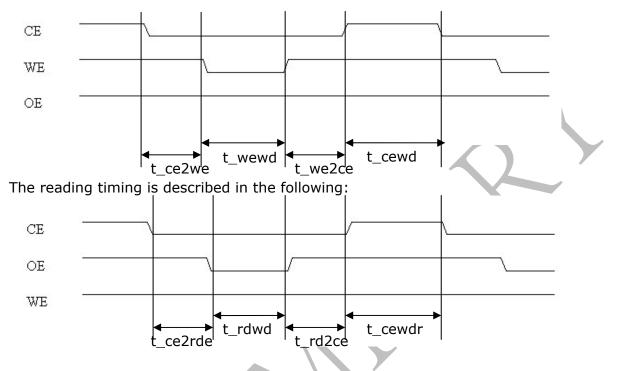

| 5.2 Architecture<br>5.2.1 Block Diagram                       |    |

| 5.2.1 Block Diagram                                           |    |

| J.Z.Z DIUCK DESCIPTIONS                                       | 72 |

|        | 5.3 Registers                                                                                                              | 39 |

|--------|----------------------------------------------------------------------------------------------------------------------------|----|

|        | 5.3.1 Registers Summary                                                                                                    | 39 |

|        | 5.3.2 Detail Register Description                                                                                          | 40 |

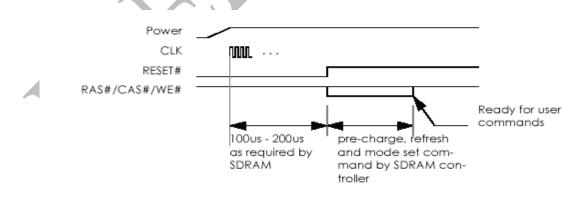

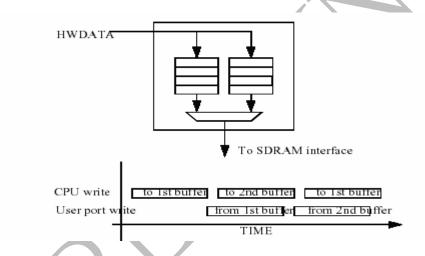

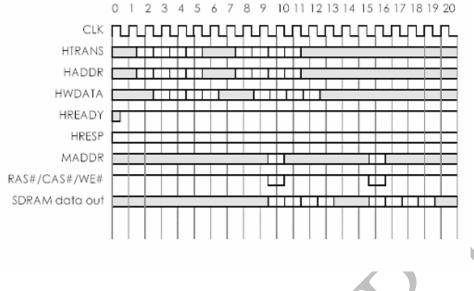

|        | 5.4 Functional Description                                                                                                 |    |

|        | 5.4.1 Memory Integration                                                                                                   |    |

|        | 5.4.2 Initialization                                                                                                       |    |

|        | 5.4.3 Operation                                                                                                            |    |

| Chanto | <sup>6</sup> Interrupt Controller                                                                                          |    |

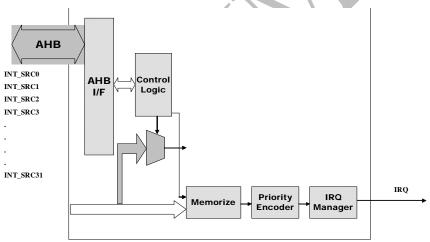

| •      | 5.1 Design Overview                                                                                                        |    |

|        | -                                                                                                                          |    |

|        | 6.1.1 Overview                                                                                                             |    |

|        | 6.1.2 Features                                                                                                             |    |

|        | 5.2 Architecture                                                                                                           |    |

|        | 6.2.1 Block Diagram                                                                                                        |    |

|        | 6.2.2 Block Descriptions                                                                                                   |    |

|        | 5.3 Registers                                                                                                              |    |

|        | 6.3.1 Registers Summary                                                                                                    | 50 |

|        | 6.3.2 Detail Register Description                                                                                          | 51 |

|        | 5.4 Functional Description                                                                                                 | 59 |

|        | 6.4.1 Operation                                                                                                            |    |

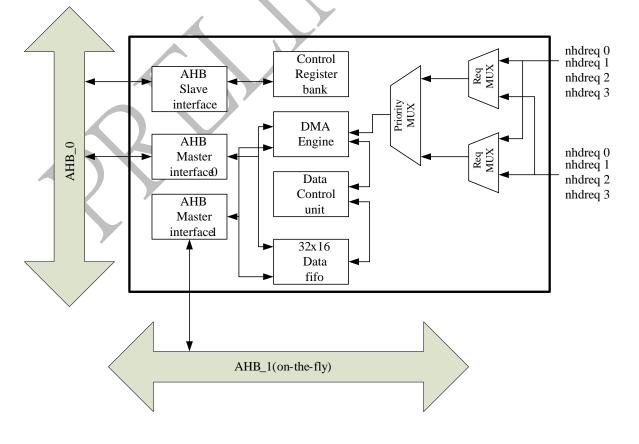

| Chapte | 7 AHB DMA (HDMA)                                                                                                           |    |

|        | 7.1 Design Overview                                                                                                        | 60 |

|        | 7.1.1 Overview                                                                                                             |    |

|        |                                                                                                                            | 60 |

|        | 7.1.2 Teatures                                                                                                             | 60 |

|        | 7.2 Architecture                                                                                                           | 60 |

|        | <ul> <li>7.1.2 Teaches</li> <li>7.2 Architecture</li> <li>7.2.1 Block Diagram</li> <li>7.2.2 Block Descriptions</li> </ul> | 60 |

|        | 7.2.2 Block Descriptions                                                                                                   | 01 |

|        | 7.3 Registers<br>7.3.1 Registers Summary                                                                                   | 61 |

|        | 7.3.1 Registers Summary                                                                                                    | 61 |

|        | 7.3.2 Detail Register Description                                                                                          | 62 |

|        | 7.4 Functional Description                                                                                                 | 66 |

|        | 7.4.1 S/W Trigger DMA Mode                                                                                                 | 66 |

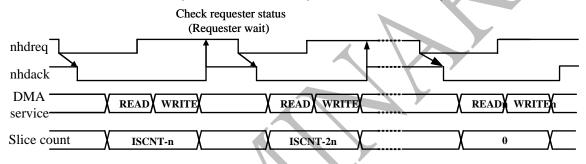

|        | 7.4.2 H/W Trigger DMA Mode                                                                                                 |    |

|        | 7.4.3 On-the-Fly DMA Mode                                                                                                  | 67 |

|        | 7.5 Application Notes                                                                                                      | 67 |

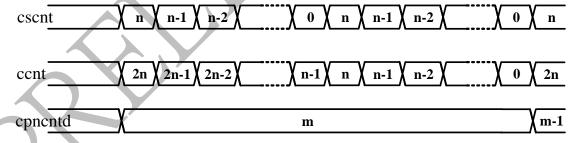

| Chapte | 8 DW DMA                                                                                                                   | 69 |

| •      | 3.1 Design Overview                                                                                                        | 69 |

|        | 8.1.1 Overview                                                                                                             |    |

|        | 8.1.2 Features                                                                                                             |    |

|        | 3.2 Architecture                                                                                                           |    |

|        | 3.3 Registers                                                                                                              |    |

|        | 8.3.1 Registers Summary                                                                                                    |    |

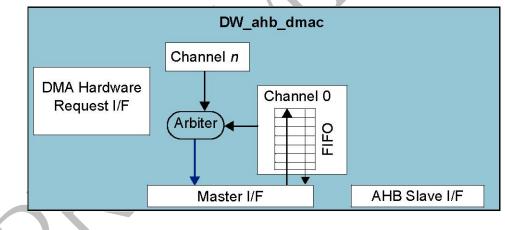

|        | 8.3.2 Configuration and Channel Enable Registers                                                                           |    |

|        | 8.3.3 Channel Registers                                                                                                    |    |

|        | 8.3.4 Interrupt Registers                                                                                                  |    |

|        |                                                                                                                            |    |

|        | 8.3.5 Software Handshaking Registers                                                                                       |    |

|        | 3.4 Register Access                                                                                                        |    |

|        | 3.5 Illegal Register Access                                                                                                |    |

|        | 3.6 DW_ahb_dmac Transfer Types                                                                                             |    |

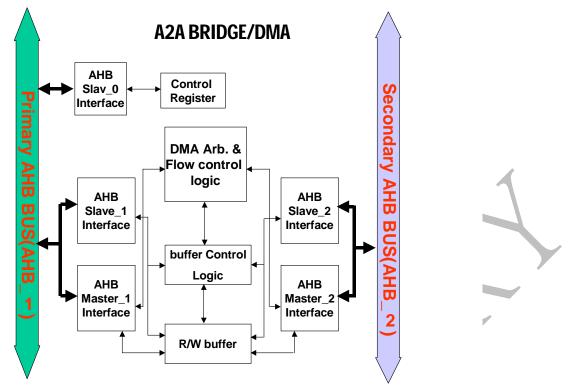

| -      | 9 AHB-to-AHB Bridge                                                                                                        |    |

|        | 9.1 Design Overview                                                                                                        |    |

|        | 9.1.1 Overview                                                                                                             |    |

|        | 9.1.2 Features                                                                                                             |    |

|        | 0.2 Architecture                                                                                                           | 97 |

|        | 9.2.1 Block Diagram                                                                                                        | 98 |

|        | 9.2.2 Block Descriptions                                                                                                   |    |

|        | 9.3 Registers                                                                                                              |    |

|        | 9.3.1 Registers Summary                                                                                                    |    |

|        | 9.3.2 Detail Register Description                                                                                          |    |

|        | 5                                                                                                                          | -  |

| 9.4 Functional Description                                                                        | 102 |

|---------------------------------------------------------------------------------------------------|-----|

| 9.4.1 AHB Bridge Mode Operation                                                                   | 102 |

| 9.4.2 AHB DMA Mode Operation                                                                      | 103 |

| 9.5 Application Notes                                                                             | 104 |

| Chapter 10 USB 2.0 Host Controller 1                                                              |     |

| 10.1 Design Overview                                                                              | 105 |

| 10.1.1 Overview                                                                                   |     |

| 10.1.2 Features                                                                                   | 105 |

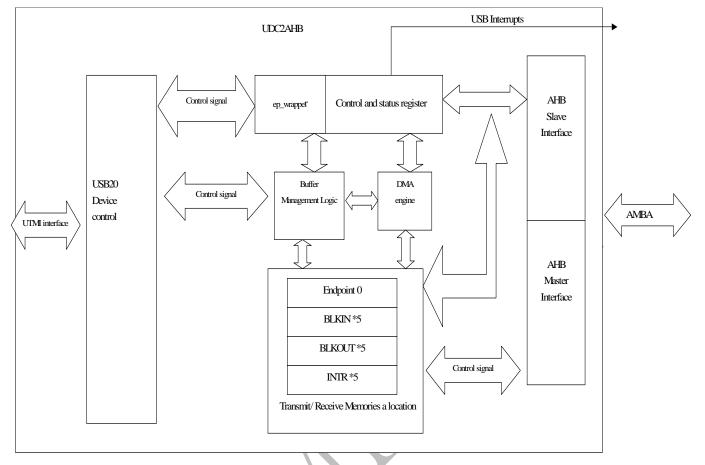

| Chapter 11 USB 2.0 Device Controller1                                                             | 106 |

| 11.1 Design Overview                                                                              | 106 |

| 11.1.1 Overview                                                                                   | 106 |

| 11.1.2 Features                                                                                   | 106 |

| 11.2 Architecture                                                                                 | 106 |

| 11.2.1 Block Diagram                                                                              | 107 |

| 11.2.2 Block Descriptions                                                                         | 107 |

| 11.3 Registers                                                                                    | 108 |

| 11.3.1 Registers Summary                                                                          | 108 |

| 11.3.2 Detail Register Description                                                                | 111 |

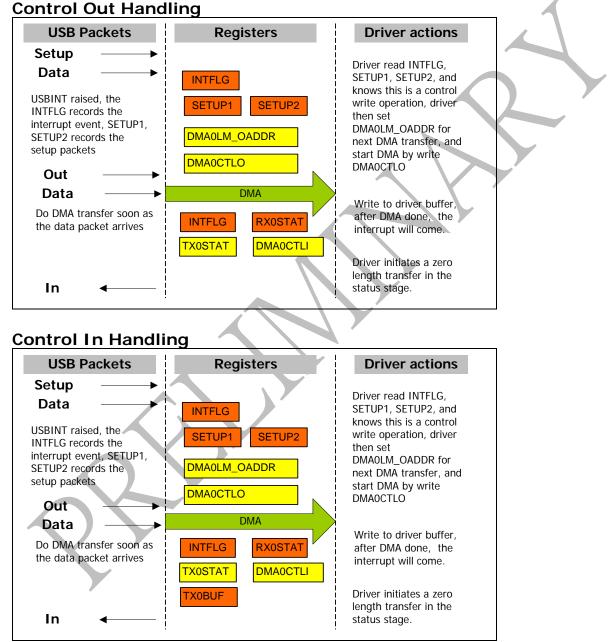

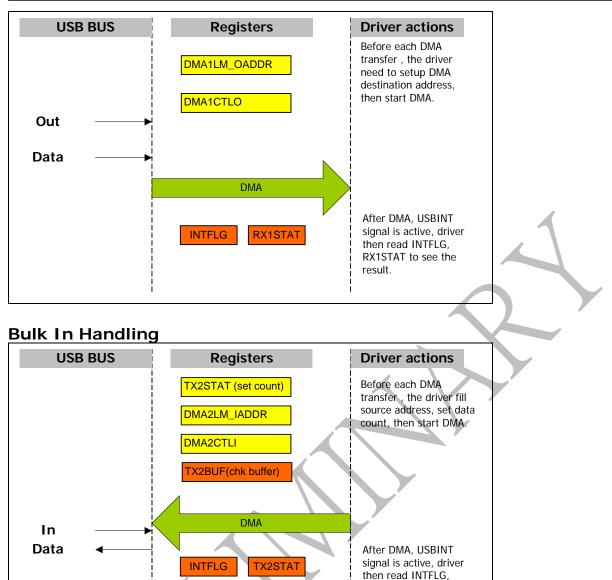

| 11.4 Functional Description                                                                       | 125 |

| 11.4.1 Operation                                                                                  | 125 |

| 11.4.2 Programming sequence                                                                       | 127 |

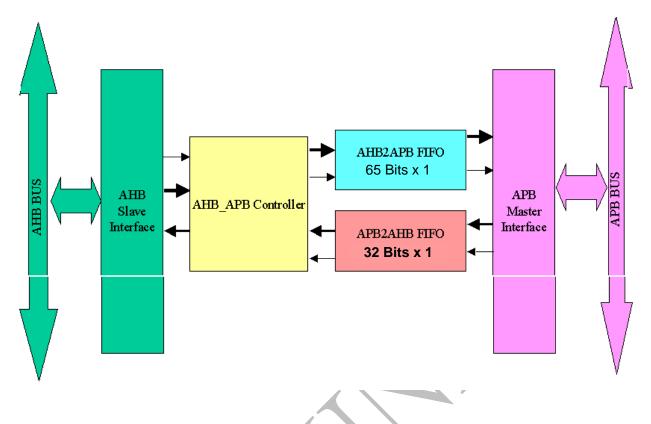

| Chapter 12 AHB-to-APB Bridge 12.1 Design Overview 12.1.1 Overview 12.1.2 Features 12.1.2 Features | 131 |

| 12.1 Design Overview                                                                              | 131 |

| 12.1.1 Overview                                                                                   | 131 |

| 12.1.2 Features                                                                                   | 131 |

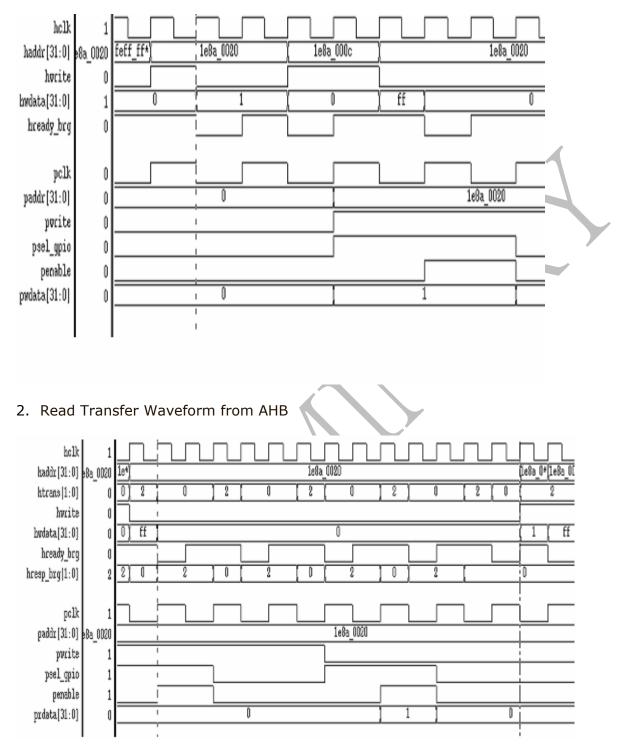

| 12.2 Architecture                                                                                 | 131 |

| 12.2.1 Block Diagram                                                                              | 132 |

| 12.2.1 Block Diagram<br>12.2.2 Block Descriptions                                                 | 132 |

| 12.3 Functional Description                                                                       | 132 |

| 12.3.1 Operation                                                                                  | 132 |

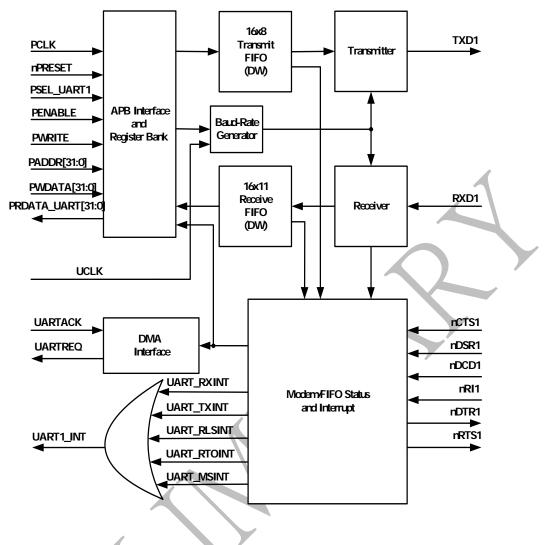

| Chapter 13 UART (16550) 1                                                                         | 135 |

| 13.1 Design Overview                                                                              | 135 |

| 13.1.1 Overview                                                                                   | 135 |

| 13.1.2 Features                                                                                   | 135 |

| 13.2 Architecture                                                                                 | 135 |

| 13.2.1 Block Diagram                                                                              | 136 |

| 13.2.2 Block Descriptions                                                                         | 136 |

| 13.3 Registers                                                                                    | 136 |

| 13.3.1 Registers Summary                                                                          | 136 |

| 13.3.2 Detail Register Description                                                                |     |

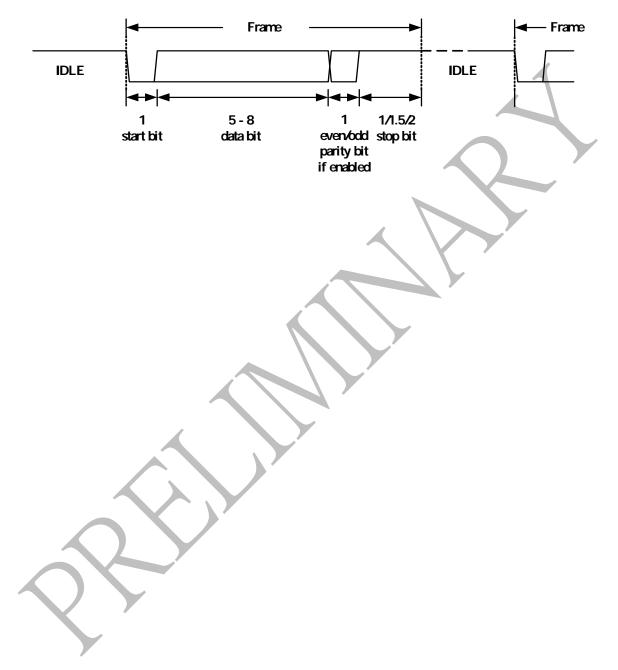

| 13.4 Functional Description                                                                       | 142 |

| 13.4.1 Clock Signals                                                                              | 142 |

| 13.4.2 Operation                                                                                  | 142 |

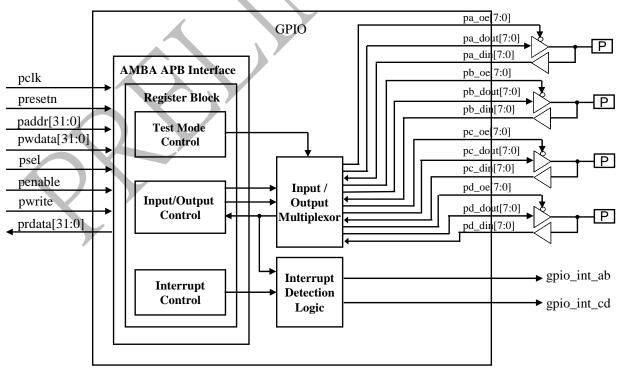

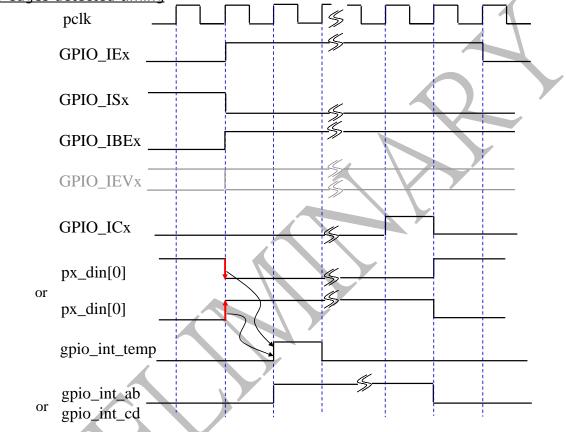

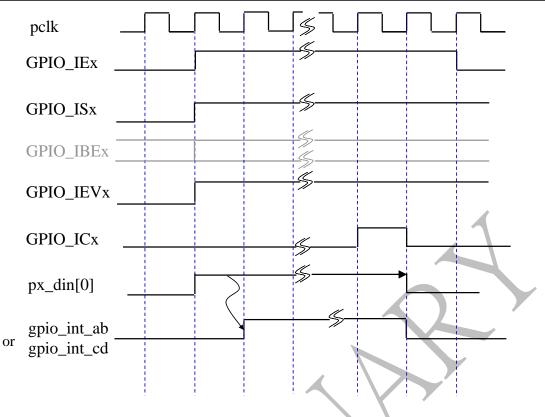

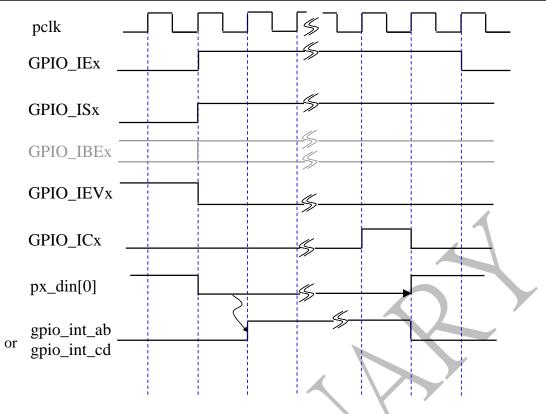

| Chapter 14 General Purpose IO (GPIO)1                                                             | 144 |

| 14.1 Design Overview                                                                              | 144 |

| 14.1.1 Overview                                                                                   |     |

| 14.1.2 Features                                                                                   | 144 |

| 14.2 Architecture                                                                                 | 144 |

| 14.2.1 Block Diagram                                                                              | 144 |

| 14.2.2 Block Descriptions                                                                         | 144 |

| 14.3 Registers                                                                                    | 145 |

| 14.3.1 Registers Summary                                                                          | 145 |

| 14.3.2 Detail Register Description                                                                |     |

| 14.4 Functional Description                                                                       |     |

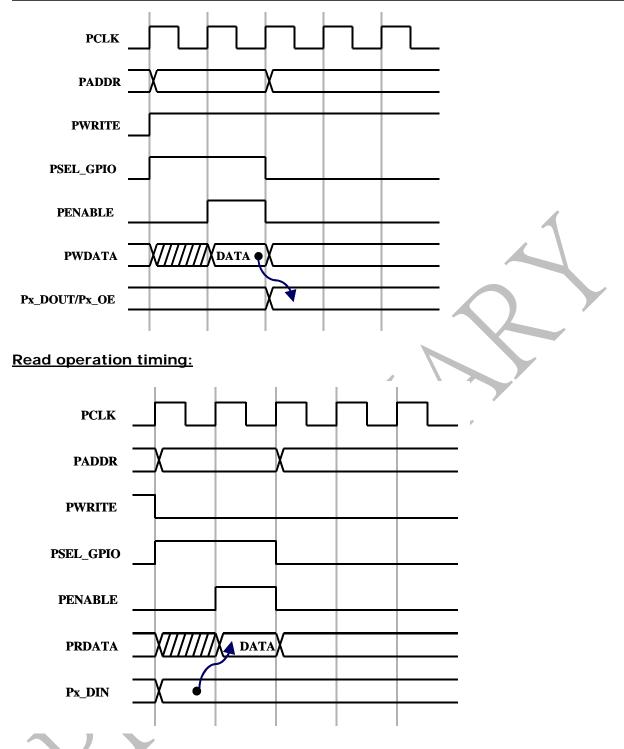

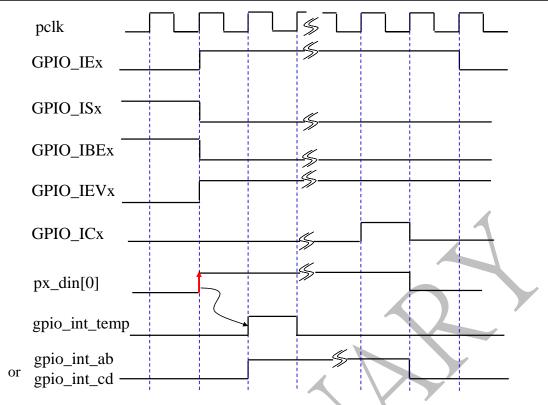

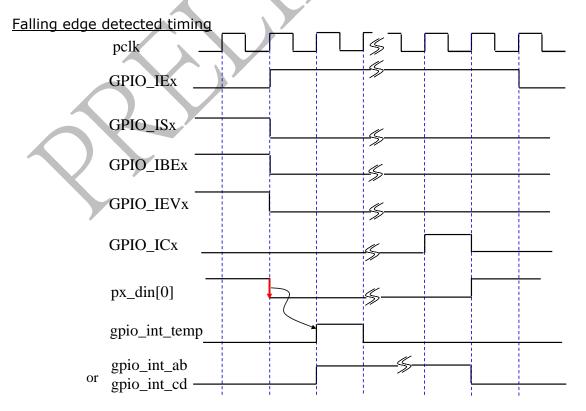

| 14.4.1 Operation                                                                                  |     |

| 14.4.2 Programming sequence                                                                       | 149 |

| 14.5 GPIO MUX                                                                                     | 153 |

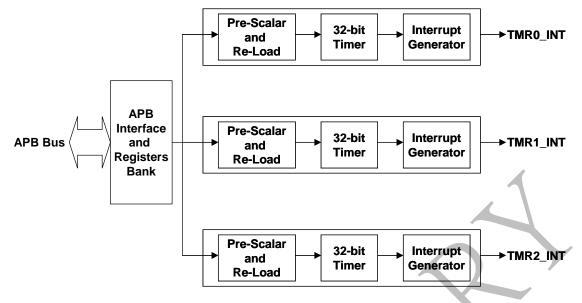

| Chapter 15 Timers 1                                                                               | 155 |

| 15.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 155                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.1.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 155                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 155                                                                                                                                                                  |

| 15.2 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 155                                                                                                                                                                  |

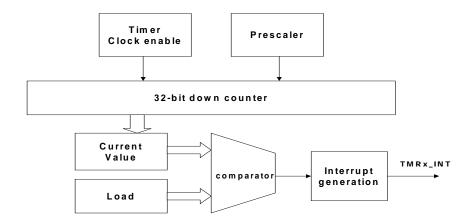

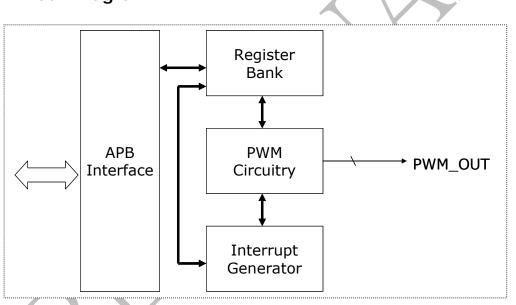

| 15.2.1 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 156                                                                                                                                                                  |

| 15.2.2 Block Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 156                                                                                                                                                                  |

| 15.3 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 156                                                                                                                                                                  |

| 15.3.1 Registers Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 156                                                                                                                                                                  |

| 15.3.2 Detail Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 15.4 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 157                                                                                                                                                                  |

| 15.4.1 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| Chapter 16 Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| 16.1 Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 159                                                                                                                                                                  |

| 16.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| 16.1.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| 16.2 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 159                                                                                                                                                                  |

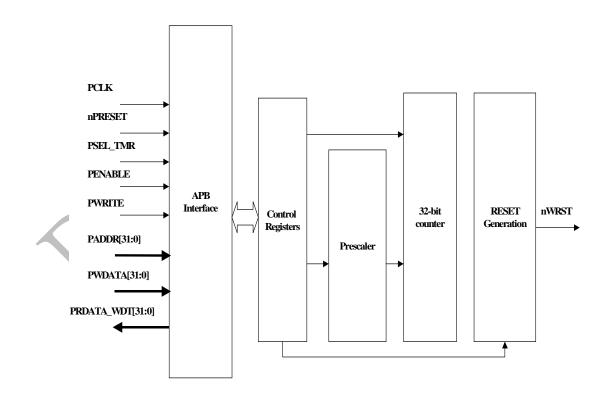

| 16.2.1 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 159                                                                                                                                                                  |

| 16.2.2 Block Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 160                                                                                                                                                                  |

| 16.3 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

| 16.3.1 Registers Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 160                                                                                                                                                                  |

| 16.3.2 Detail Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 160                                                                                                                                                                  |

| 16.4 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 161                                                                                                                                                                  |

| 16.4.1 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 161                                                                                                                                                                  |

| 16.4 Functional Description<br>16.4.1 Operation<br>Chapter 17 Real Time Clock (RTC)<br>17.1 Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 162                                                                                                                                                                  |

| 17.1 Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 162                                                                                                                                                                  |

| 17.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 102                                                                                                                                                                  |

| 17.1.2 Features<br>Chapter 18 SPI Master Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 162                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 162                                                                                                                                                                  |

| Chapter 18 SPI Master Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                                                                                                                  |

| 18.1 Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 163                                                                                                                                                                  |

| 18.1 Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 163<br>163                                                                                                                                                           |

| 18.1       Design Overview         18.1.1       Overview         18.1.2       Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 163<br>163<br>163                                                                                                                                                    |

| <ul> <li>18.1 Design Overview</li> <li>18.1.1 Overview</li> <li>18.1.2 Features</li> <li>18.2 Architecture</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 163<br>163<br>163<br>163                                                                                                                                             |

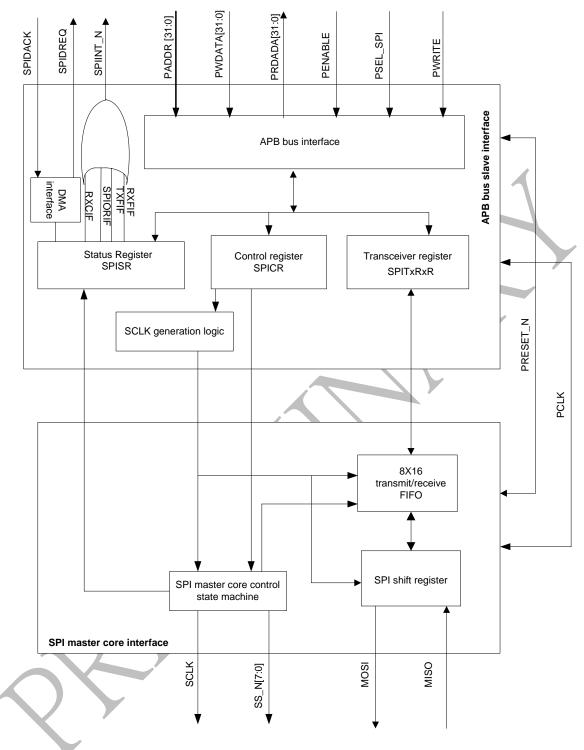

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>163<br>164                                                                                                                                      |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>163<br>164<br>164                                                                                                                               |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>163<br>164<br>164<br>164                                                                                                                        |

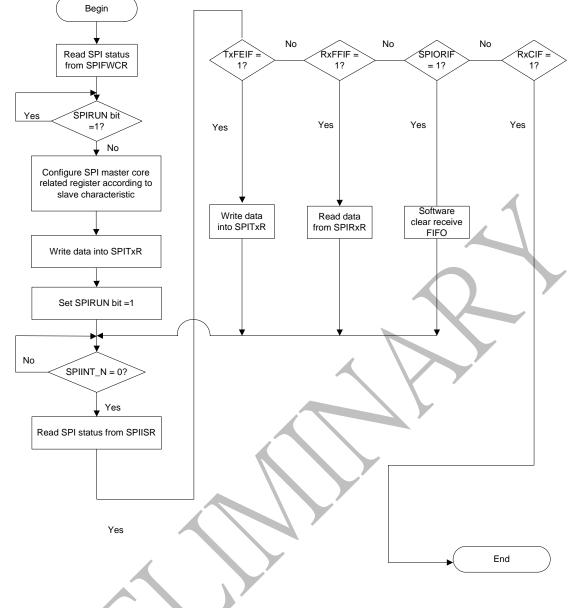

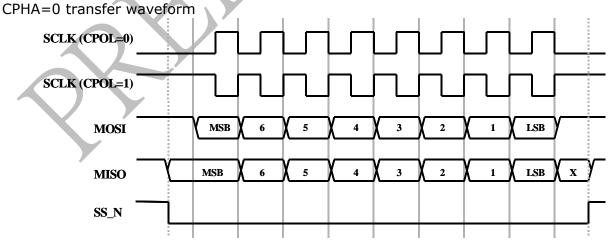

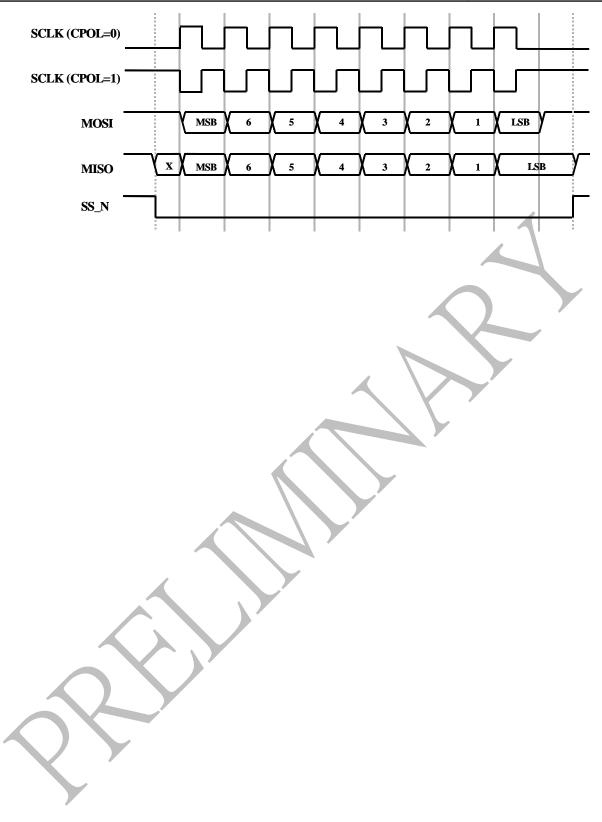

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165                                                                                                                 |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>163</li> <li>163</li> <li>163</li> <li>164</li> <li>164</li> <li>164</li> <li>165</li> <li>165</li> </ul>                                                   |

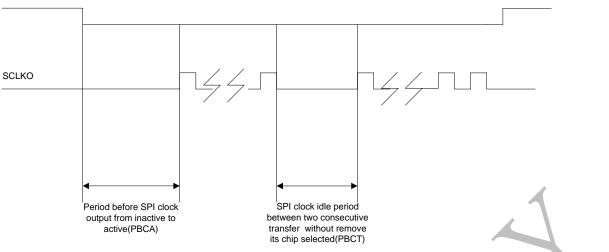

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170                                                                                                          |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>163</li> <li>163</li> <li>163</li> <li>164</li> <li>164</li> <li>164</li> <li>165</li> <li>165</li> <li>170</li> <li>170</li> </ul>                         |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>163</li> <li>163</li> <li>163</li> <li>164</li> <li>164</li> <li>164</li> <li>165</li> <li>165</li> <li>170</li> <li>170</li> <li>173</li> </ul>            |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>165<br>170<br>170<br><b>173</b><br>173                                                                       |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>163</li> <li>163</li> <li>163</li> <li>164</li> <li>164</li> <li>165</li> <li>165</li> <li>170</li> <li>170</li> <li>173</li> <li>173</li> </ul>            |

| <ul> <li>18.1 Design Overview</li> <li>18.1.1 Overview</li> <li>18.1.2 Features</li> <li>18.2 Architecture</li> <li>18.2.1 Block Diagram</li> <li>18.2.2 Block Descriptions</li> <li>18.3 Registers</li> <li>18.3.1 Registers Summary</li> <li>18.3.2 Detail Register Description</li> <li>18.4 Functional Description</li> <li>18.4.1 Operation</li> <li>18.4.1 Operation</li> <li>19.1 Design Overview</li> <li>19.1.1 Overview</li> <li>19.1.2 Features</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170<br>170<br>173<br>173<br>173                                                                              |

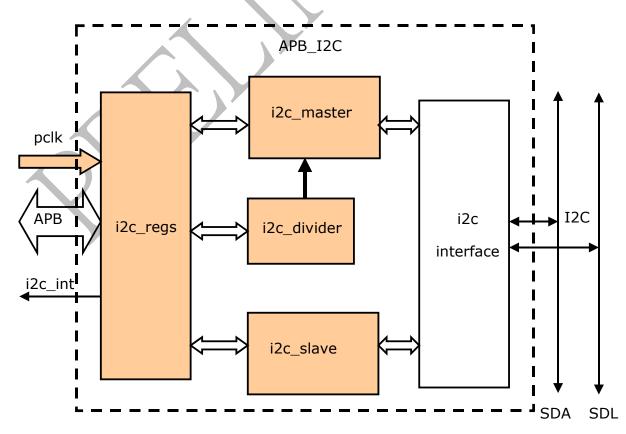

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170<br>170<br>173<br>173<br>173<br>173                                                                       |

| <ul> <li>18.1 Design Overview</li> <li>18.1.1 Overview</li> <li>18.1.2 Features</li> <li>18.2 Architecture</li> <li>18.2 Architecture</li> <li>18.2.1 Block Diagram</li> <li>18.2.2 Block Descriptions</li> <li>18.3 Registers</li> <li>18.3.1 Registers Summary</li> <li>18.3.2 Detail Register Description</li> <li>18.4 Functional Description</li> <li>18.4.1 Operation</li> <li>Chapter 19 I2C Controller</li> <li>19.1 Design Overview</li> <li>19.1.2 Features</li> <li>19.2 Architecture</li> <li>19.2.1 Block Diagram</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170<br>170<br>173<br>173<br>173<br>173<br>173                                                                |

| <ul> <li>18.1 Design Overview</li> <li>18.1.1 Overview</li> <li>18.1.2 Features</li> <li>18.2 Architecture</li> <li>18.2.1 Block Diagram</li> <li>18.2.2 Block Descriptions</li> <li>18.3 Registers</li> <li>18.3.1 Registers Summary</li> <li>18.3.2 Detail Register Description</li> <li>18.4 Functional Description</li> <li>18.4.1 Operation</li> <li>Chapter 19 I2C Controller</li> <li>19.1 Design Overview</li> <li>19.1.2 Features</li> <li>19.2 Architecture</li> <li>19.2 Block Diagram</li> <li>19.2.1 Block Diagram</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>173                                                  |

| 18.1 Design Overview         18.1.1 Overview         18.1.2 Features         18.2 Architecture         18.2 Architecture         18.2.1 Block Diagram         18.2.2 Block Descriptions         18.3 Registers         18.3.1 Registers Summary         18.3.2 Detail Register Description         18.4 Functional Description         18.4.1 Operation         18.4.1 Operation         19.1 Design Overview         19.1.1 Overview         19.2 Features         19.2 Architecture         19.2.1 Block Diagram         19.2.2 Block Descriptions         19.3 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>173                                                         |

| <ul> <li>18.1 Design Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 163<br>163<br>163<br>164<br>164<br>164<br>165<br>165<br>170<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>174<br>174                                           |