# RK28XX Technical Reference Manual

# Revision 0.1

Rockchip Feb 2009

# **Revision History**

| Date       | Revision | Description                                                                                                                                                                                           |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2009-02-18 | 0.1      | Frist release                                                                                                                                                                                         |

| 2009-03-20 | 0.2      | Host interface bypass to lcdc modified<br>Modify error for Pull Up or Down register set<br>Modify Chapter 31 GPIO Pull Up or Pull Down setting<br>Modify LCDC Port MUX List<br>Add RK2808 description |

|            |          |                                                                                                                                                                                                       |

# TABLE OF CONTENT

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 2                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| TABLE OF CONTENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 3                                                                  |

| Figure Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                   |

| Table Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                   |

| Acronym descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                   |

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14                                                                   |

| 1.1 OVERVIEW<br>1.2 FEATURES<br>1.3 BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14                                                                   |

| Chapter 2 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                                   |

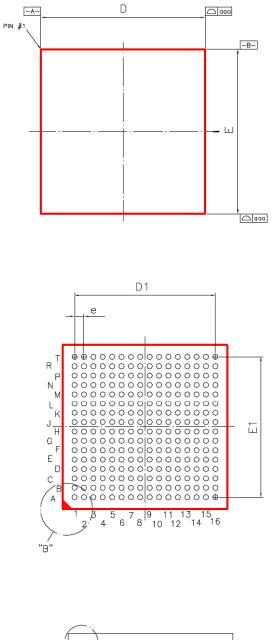

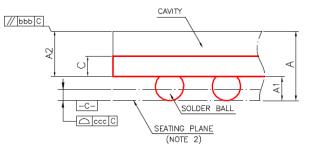

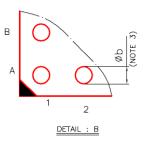

| 2.1 RK2806 PIN PLACEMENT<br>2.2 RK2806 PIN DESCRIPTION<br>2.3 BGA256 PACKAGE OUTLINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22<br>28                                                             |

| Chapter 3 System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29                                                                   |

| 3.1 BUS ARCHITECTURE.         3.1.1 CPU SYSTEM AHB BUS ARCHITECTURE.         3.1.2 DSP SYSTEM AHB BUS ARCHITECTURE.         3.1.3 DATA PATH DESCRIPTION FOR CPU AND DSP.         3.1.4 CPU ITCM/DTCM APPLICATION NOTES.         3.1.5 SDRAM AND MOBILE SDRAM INTERFACE APPLICATION NOTES.         3.2 SYSTEM ADDRESS MAP.         3.2.1 SYSTEM MEMORY MAP FOR CPU         3.3 SYSTEM MODE CONFIGURATION.         3.3.1 DEBUG MODE         3.3.2 CPU BOOT MODE.         3.4 SYSTEM INTERRUPT CONNECTION .         3.5 SYSTEM DMA HARDWARE REQUEST CONNECTION. | 29<br>29<br>31<br>32<br>33<br>33<br>34<br>35<br>35<br>35<br>35<br>37 |

| Chapter 4 Static/SDRAM Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 4.1 DESIGN OVERVIEW4.1.1 OVERVIEW4.1.2 FEATURES4.2 ARCHITECTURE4.2.1 OVERVIEW4.2.2 BLOCK DESCRIPTIONS4.3 REGISTERS4.3.1 REGISTERS SUMMARY4.3.2 DETAIL REGISTER DESCRIPTION4.4 FUNCTIONAL DESCRIPTION4.4.1 OPERATION                                                                                                                                                                                                                                                                                                                                          | 39<br>39<br>40<br>40<br>41<br>41<br>41<br>41                         |

| Chapter 5 Static/Mobile SDRAM Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                                   |

| 5.1 DESIGN OVERVIEW<br>5.1.1 OVERVIEW<br>5.1.2 FEATURES<br>5.2 ARCHITECTURE<br>5.2.1 OVERVIEW<br>5.2.2 BLOCK DESCRIPTIONS<br>5.3 REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                   | 57<br>57<br>57<br>57<br>58<br>58                                     |

| 5.3.1 REGISTERS SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9<br>7          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Chapter 6 NAND Flash Controller 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5               |

| 6.1 DESIGN OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5<br>5          |

| Chapter 7 SD/MMC Host Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5               |

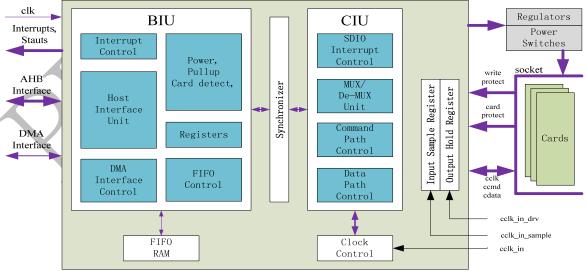

| 7.1 DESIGN OVERVIEW       76         7.1.1 OVERVIEW       76         7.1.2 FEATURES       76         7.2 ARCHITECTURE       76         7.2.1 BLOCK DIAGRAM       76         7.2.2 BLOCK DESCRIPTIONS       76         7.3 REGISTERS       88         7.3.1 REGISTERS SUMMARY       88         7.3.2 DETAIL REGISTER DESCRIPTION       88         7.4 FUNCTIONAL DESCRIPTION       99         7.4.1 OPERATION       99                                                                                                                                                                                                                                                                                                                   | 5555588899      |

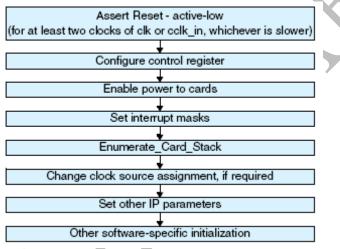

| 7.4.2 PROGRAMMING SEQUENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3               |

| 8.1 DESIGN OVERVIEW       113         8.1.1 OVERVIEW       113         8.1.2 FEATURES       113         8.2 ARCHITECTURE       113         8.2.1 BLOCK DIAGRAM       113         8.3 REGISTERS       113         8.3.1 REGISTERS SUMMARY       113         8.3.2 DETAIL REGISTER DESCRIPTION       114         8.4 FUNCTIONAL DESCRIPTION       118         8.4.1 OPERATION       118                                                                                                                                                                                                                                                                                                                                                   | 3333333438      |

| Chapter 9 LCD Controller 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1               |

| 9.1 DESIGN OVERVIEW       121         9.1.1 OVERVIEW       121         9.1.2 FEATURES       121         9.2 ARCHITECTURE       121         9.2.1 OVERVIEW       121         9.2.2 BLOCK DESCRIPTION       121         9.3 REGISTER DEFINITION       121         9.3.1 REGISTER DEFINITION       121         9.3.2 DETAILED REGISTER DESCRIPTION       122         9.4 FUNCTION DESCRIPTION       123         9.4.1 BUS OPERATION       134         9.4.2 BUS OPERATION CONFIGURE       134         9.4.3 DISPLAY OPERATION CONFIGURE       135         9.4.4 DISPLAY TIMING       136         9.4.5 LCDC INPUT DATA FORMAT       137         8.4.6 LCDC OUTPUT DATA FORMAT       138         9.4.7 LCDC PIN TABLE DESCRIPTION       139 | 111111134445678 |

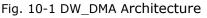

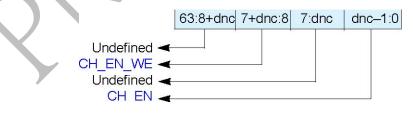

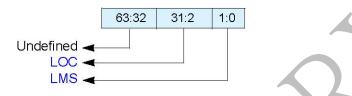

| Chapter 10 DW_DMA 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )               |

| 10.1 DESIGN OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

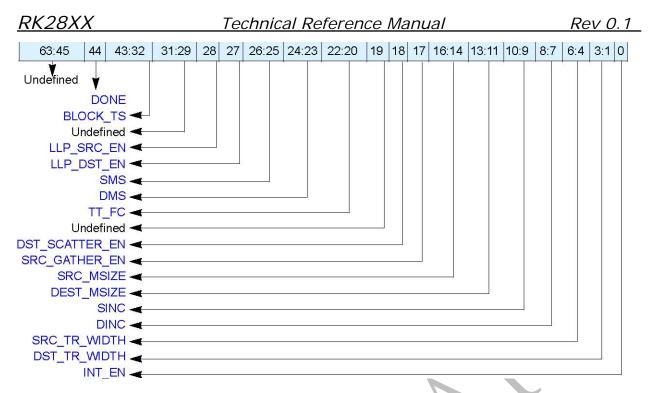

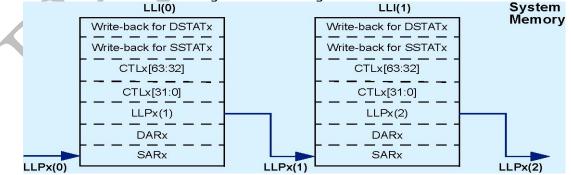

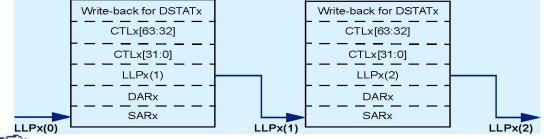

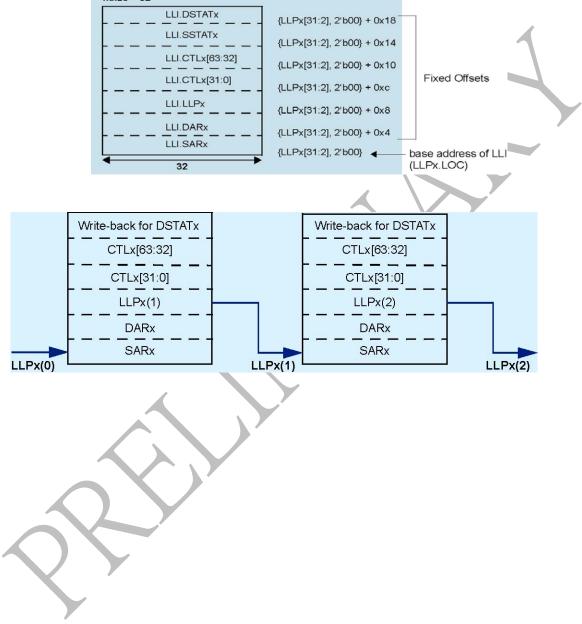

| 10.1.2 FEATURES<br>10.2 ARCHITECTURE<br>10.3 REGISTERS<br>10.3.1 REGISTERS SUMMARY<br>10.3.2 CONFIGURATION AND CHANNEL ENABLE REGISTERS<br>10.3.3 CHANNEL REGISTERS<br>10.3.4 INTERRUPT REGISTERS<br>10.4 REGISTER ACCESS<br>10.5 ILLEGAL REGISTER ACCESS<br>10.6 DW_DMA TRANSFER TYPES | 140<br>140<br>142<br>143<br>153<br>157<br>157                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Chapter 11 XDMA                                                                                                                                                                                                                                                                         |                                                                           |

| 11.1 OVERVIEW                                                                                                                                                                                                                                                                           | 161                                                                       |

| Chapter 12 Interrupt Controller (INTC)                                                                                                                                                                                                                                                  | 162                                                                       |

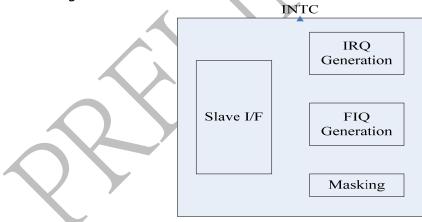

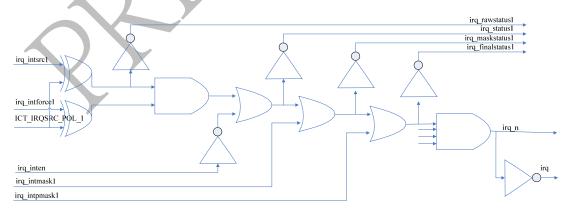

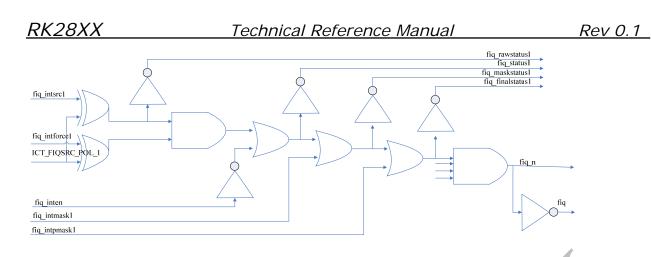

| 12.1 DESIGN OVERVIEW<br>12.1.1 OVERVIEW<br>12.1.2 FEATURES<br>12.2 ARCHITECTURE<br>12.2.1 BLOCK DIAGRAM<br>12.3 REGISTERS<br>12.3.1 REGISTERS SUMMARY<br>11.3.2 DETAIL REGISTER DESCRIPTION<br>12.4 FUNCTIONAL DESCRIPTION<br>12.4.1 OVERVIEW<br>12.4.2 DETAIL DESCRIPTION              | 162<br>162<br>162<br>162<br>162<br>162<br>162<br>163<br>168<br>168<br>168 |

| Chapter 13 High-Speed ADC Interface                                                                                                                                                                                                                                                     | 171                                                                       |

| 13.1 DESIGN OVERVIEW<br>13.1.1 OVERVIEW<br>13.1.2 FEATURES                                                                                                                                                                                                                              | 171                                                                       |

| 13.1.2 FEATURES                                                                                                                                                                                                                                                                         | 172                                                                       |

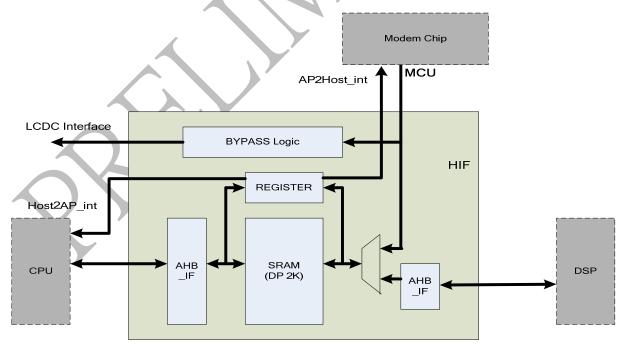

| 14.1 DESIGN OVERVIEW<br>14.1.1 OVERVIEW<br>14.1.2 FEATURES<br>14.2 ARCHITECTURE<br>14.2.1 BLOCK DIAGRAM<br>14.3 REGISTERS<br>14.3.1 REGISTERS SUMMARY<br>14.3.2 DETAIL REGISTER DESCRIPTION<br>14.4 APPLICATION NOTES                                                                   | 172<br>172<br>172<br>172<br>172<br>173<br>173                             |

| Chapter 15 USB OTG Controller                                                                                                                                                                                                                                                           | 176                                                                       |

| 15.1 DESIGN OVERVIEW<br>15.1.1 OVERVIEW<br>15.1.2 FEATURES                                                                                                                                                                                                                              | 176<br>176                                                                |

| Chapter 16 System Control Unit (SCU)                                                                                                                                                                                                                                                    | 177                                                                       |

| <ul> <li>16.1 DESIGN OVERVIEW</li> <li>16.1.1 OVERVIEW</li> <li>16.1.2 KEY FEATURES</li> <li>16.2 REGISTERS</li> <li>16.2.1 REGISTERS SUMMARY</li> <li>16.2.2 DETAIL REGISTER DESCRIPTION</li> <li>16.3 APPLICATION NOTES</li> <li>16.3.1 PLL USAGE</li> </ul>                          | 177<br>177<br>177<br>177<br>178<br>185                                    |

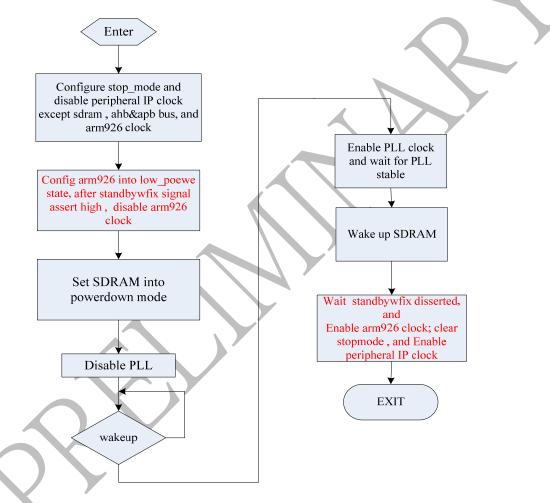

| 16.3.2 POWER MODE MANAGEMENT                                                                                                                                                                                                                                                                                                     | 186                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 17 PMU in CPU System                                                                                                                                                                                                                                                                                                     | 189                                                                                                                                          |

| <ul> <li>17.1 DESIGN OVERVIEW</li> <li>17.1.1 OVERVIEWS</li> <li>17.1.2 FEATURES</li> <li>17.2 POWER DOMAIN ARCHITECTURE</li> <li>17.3 REGISTERS</li> </ul>                                                                                                                                                                      | 189<br>189<br>189<br>190                                                                                                                     |

| Chapter 18 Processor Interface Unit (PIU)                                                                                                                                                                                                                                                                                        | 191                                                                                                                                          |

| <ul> <li>18.1 OVERVIEW</li> <li>18.1.1 OVERVIEW</li> <li>18.1.2 FEATURES</li> <li>18.2 REGISTERS</li> <li>18.2.1 REGISTERS SUMMARY</li> <li>19.2.2 DETAIL REGISTERS DESCRIPTION</li> <li>18.3 OPERATION</li> <li>18.3.1 SEMAPHORE PROTOCOL</li> <li>18.3.2 ADDRESS SNOOPING MECHANISM</li> <li>18.4 APPLICATION NOTES</li> </ul> | 191<br>191<br>191<br>192<br>200<br>200<br>200<br>201                                                                                         |

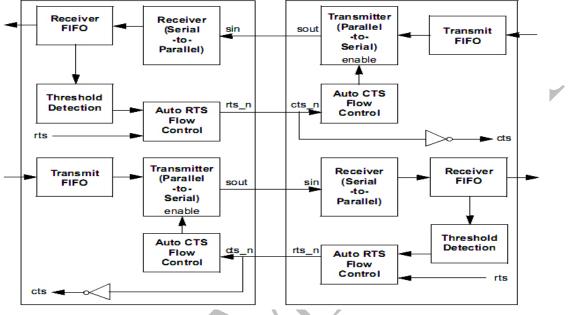

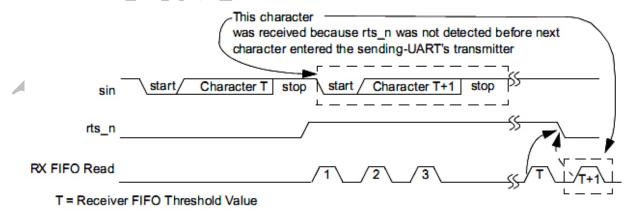

| Chapter 19 UART                                                                                                                                                                                                                                                                                                                  | 202                                                                                                                                          |

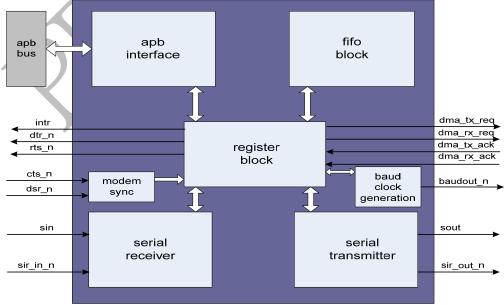

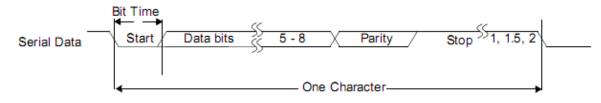

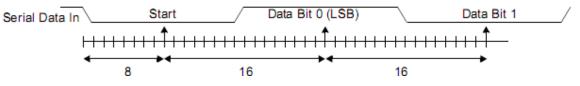

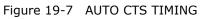

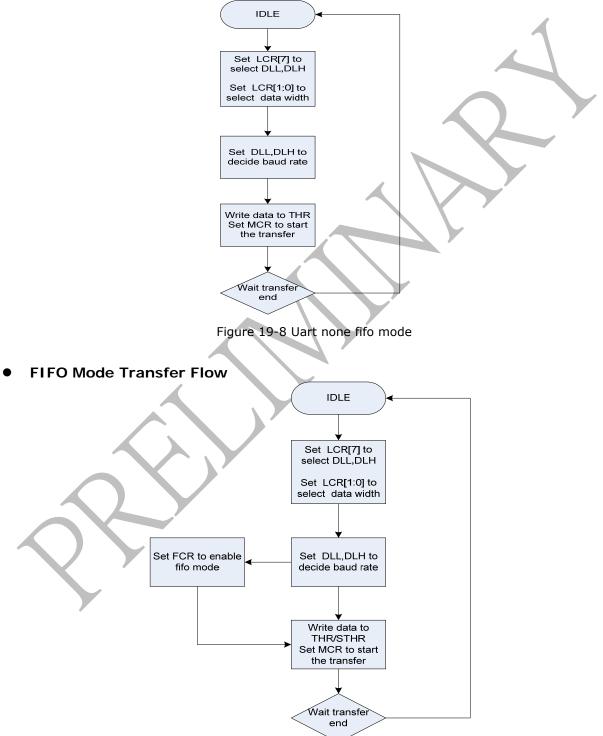

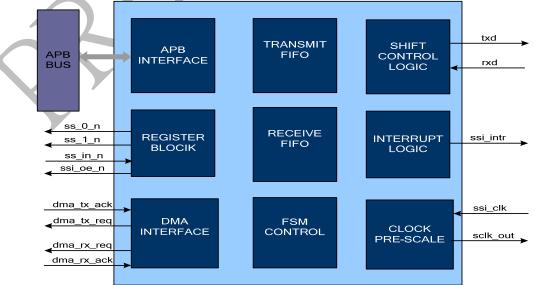

| 19.1 DESIGN OVERVIEW<br>19.1.1 OVERVIEW<br>19.1.2 FEATURES<br>19.2 ARCHITECTURE<br>19.2.1 BLOCK DIAGRAM<br>19.2.2 BLOCK DESCRIPTIONS<br>19.3 REGISTERS<br>19.3.1 REGISTERS SUMMARY<br>19.3.2 DETAIL REGISTER DESCRIPTION<br>19.4 FUNCTIONAL DESCRIPTION<br>19.4.1 OPERATION<br>19.4.2 PROGRAMMING SEQUENCE                       | 202<br>202<br>202<br>203<br>203<br>203<br>203<br>204<br>214<br>214<br>217                                                                    |

| Chapter 20 SPI Master Controller                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| 20.1 DESIGN OVERVIEW                                                                                                                                                                                                                                                                                                             | <ul> <li>219</li> <li>219</li> <li>219</li> <li>220</li> <li>220</li> <li>220</li> <li>221</li> <li>228</li> <li>228</li> <li>228</li> </ul> |

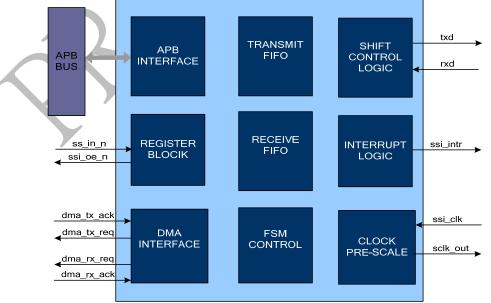

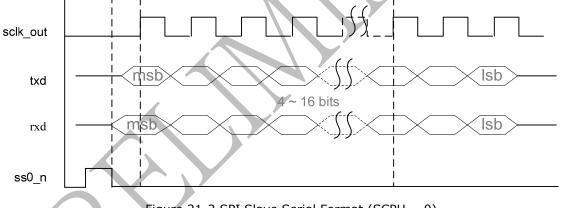

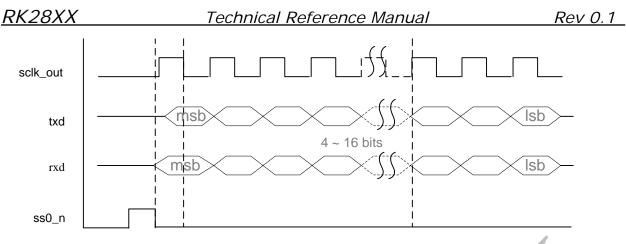

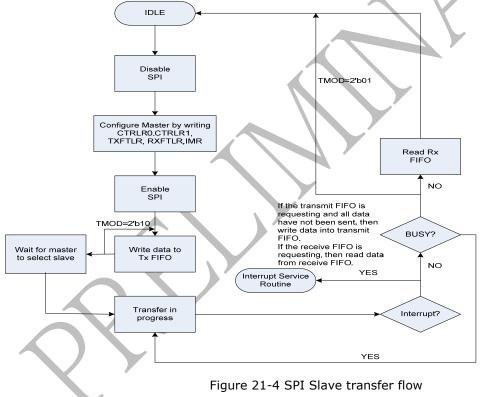

| Chapter 21 SPI Slave Controller                                                                                                                                                                                                                                                                                                  | 230                                                                                                                                          |

| 21.1 DESIGN OVERVIEW<br>21.1.1 OVERVIEW<br>21.1.2 FEATURES<br>21.2 ARCHITECTURE<br>21.2.1 BLOCK DIAGRAM<br>21.2.2 BLOCK DESCRIPTIONS<br>21.3 REGISTERS<br>21.3.1 REGISTERS SUMMARY                                                                                                                                               | 230<br>230<br>230<br>230<br>231<br>231                                                                                                       |

| 21.3.2 DETAIL REGISTER DESCRIPTION<br>21.4 FUNCTIONAL DESCRIPTION<br>21.4.1 OPERATION<br>21.4.2 PROGRAMMING SEQUENCE | 238<br>238 |

|----------------------------------------------------------------------------------------------------------------------|------------|

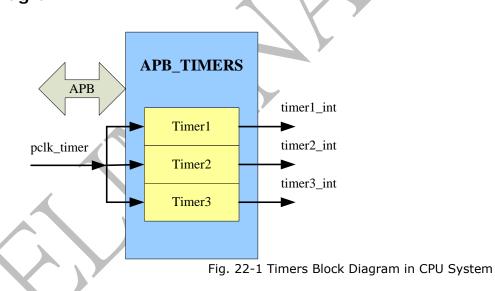

| Chapter 22 Timers in CPU system                                                                                      |            |

| 22.1 DESIGN OVERVIEW                                                                                                 | 241        |

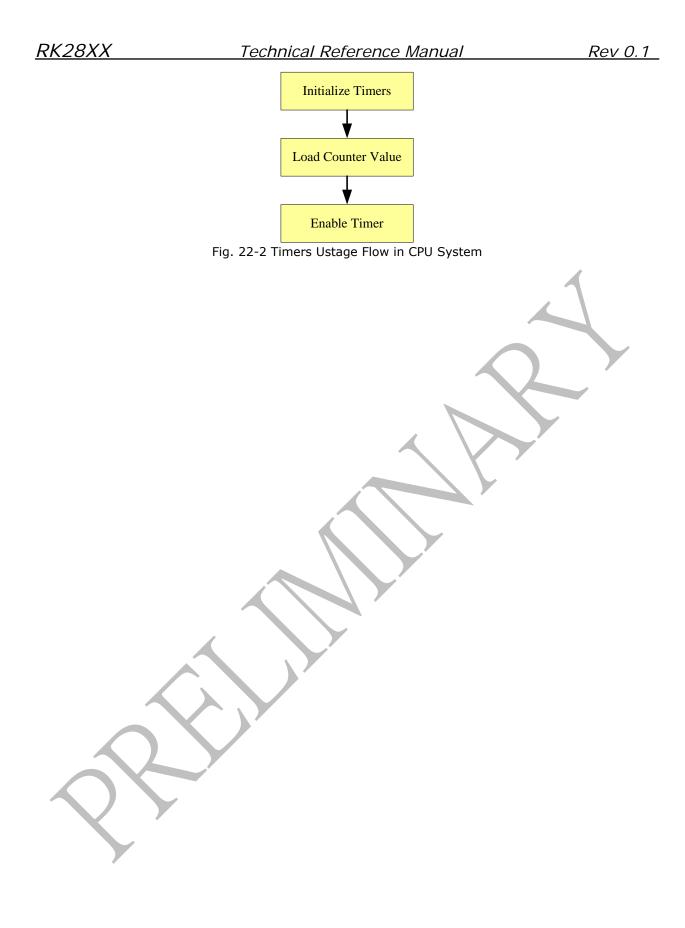

| 22.1.2 FEATURES<br>22.2 ARCHITECTURE                                                                                 | 241        |

| 22.3 REGISTERS                                                                                                       | 241<br>241 |

| 22.3.2 DETAIL REGISTER DESCRIPTION                                                                                   | 245<br>245 |

| 22.4.2 PROGRAMMING SEQUENCE                                                                                          | 245        |

| 23.1 DESIGN OVERVIEW                                                                                                 | 247        |

| 23.1.1 OVERVIEW                                                                                                      | 247        |

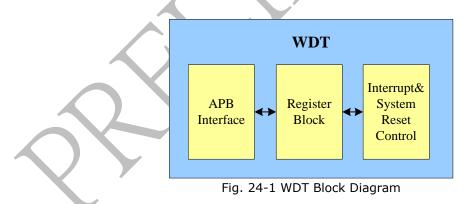

| 23.1.2 FEATURES<br>Chapter 24 Watchdog Timer (WDT)                                                                   | 247        |

| 24.1 DESIGN OVERVIEW                                                                                                 | 240        |

| 24.1.1 OVERVIEW                                                                                                      | 248        |

| 24.1.2 FLATORES<br>24.2 ARCHITECTURE<br>24.2.1 BLOCK DIAGRAM                                                         | 248        |

| 24.2.2 BLOCK DESCRIPTIONS                                                                                            | 248<br>249 |

| 24.3.1 REGISTERS SUMMARY<br>24.3.2 DETAIL REGISTER DESCRIPTION                                                       | 249        |

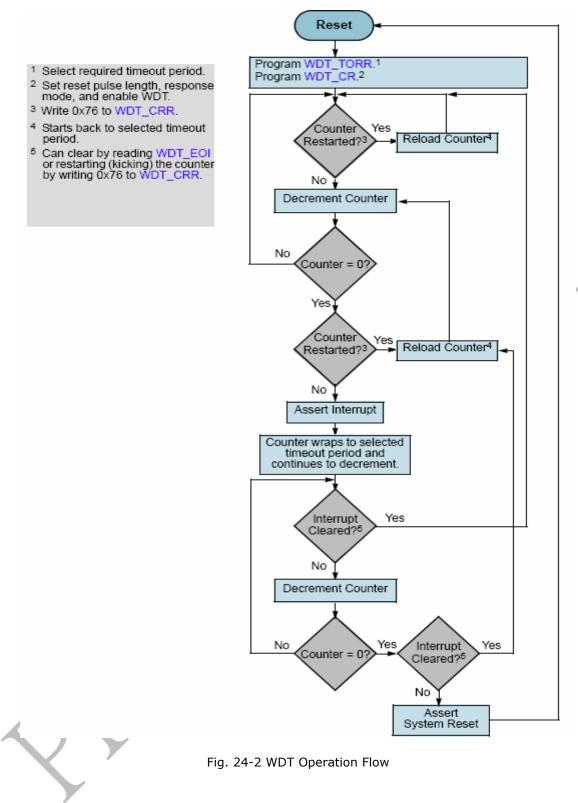

| 24.4 FUNCTIONAL DESCRIPTION                                                                                          | 251        |

| 24.4.2 PROGRAMMING SEQUENCE                                                                                          | 251        |

| Chapter 25 Real Time Clock (RTC)                                                                                     |            |

| 25.1 DESIGN OVERVIEW<br>25.1.1 OVERVIEW                                                                              | 253        |

| 25.1.2 FEATURES                                                                                                      | 253<br>253 |

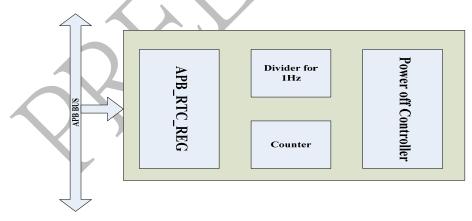

| 25.2.1 BLOCK DIAGRAM                                                                                                 | 253        |

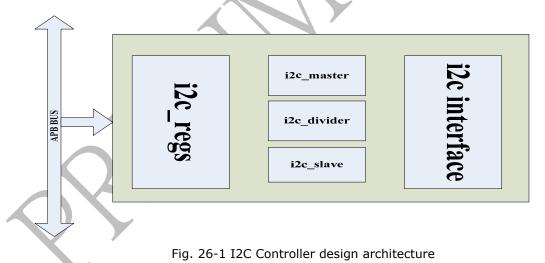

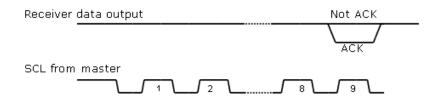

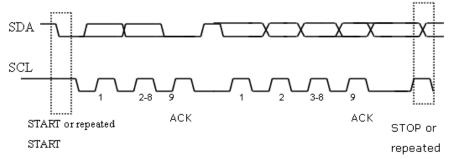

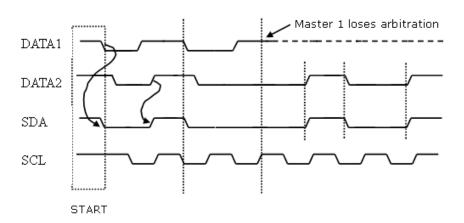

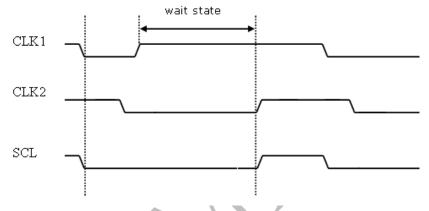

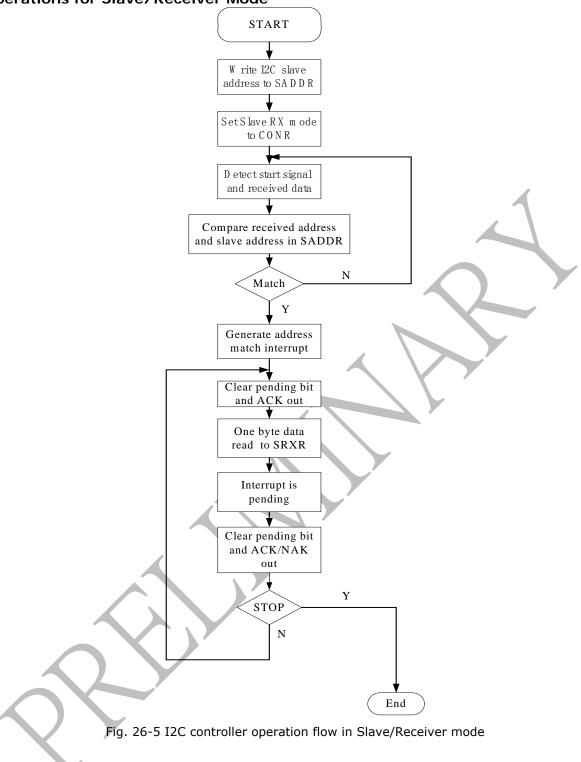

| Chapter 26 I2C Controller                                                                                            |            |

| 26.1 DESIGN OVERVIEW                                                                                                 | -          |

| 26.1.2 FEATURES                                                                                                      | 254        |

| 26.2 ARCHITECTURE                                                                                                    |            |

| 26.2.2 BLOCK DESCRIPTIONS                                                                                            |            |

| 26.3 REGISTERS                                                                                                       |            |

| 26.3.2 DETAIL REGISTER DESCRIPTION                                                                                   |            |

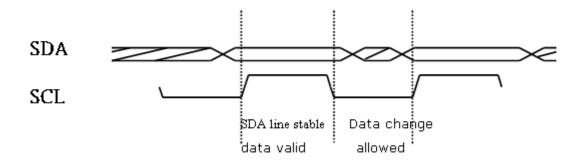

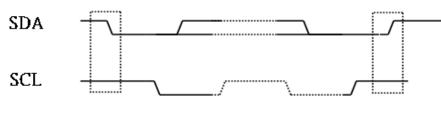

| 26.4 FUNCTIONAL DESCRIPTION<br>26.4.1 OPERATION<br>26.4.2 PROGRAMMING SEQUENCE                                       | 259        |

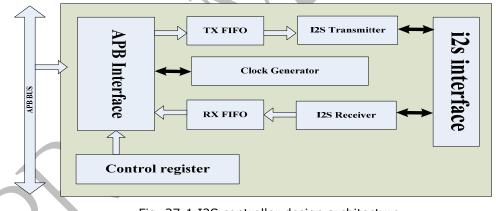

| Chapter 27 I2S Controller                                                                                            |            |

| 27.1 DESIGN OVERVIEW                                           | 268 |

|----------------------------------------------------------------|-----|

| 27.1.1 OVERVIEW                                                |     |

| 27.1.2 FEATURES                                                |     |

| 27.2 ARCHITECTURE                                              |     |

| 27.2.1 BLOCK DIAGRAM                                           |     |

| 27.2.2 BLOCK DESCRIPTIONS                                      |     |

| 27.3 REGISTERS                                                 |     |

| 27.3.1 REGISTERS SUMMARY                                       |     |

| 27.4 FUNCTIONAL DESCRIPTION                                    |     |

| 27.4.1 OPERATION                                               |     |

| 27.4.2 PROGRAMMING SEQUENCE                                    |     |

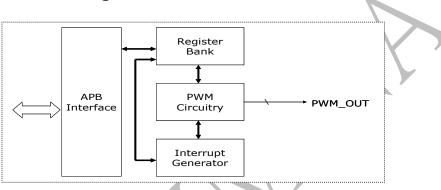

| Chapter 28 PWM Timer                                           | 278 |

| 28.1 OVERVIEW                                                  | 278 |

| 28.1.1 KEY FEATURES                                            | 278 |

| 28.2 ARCHITECTURE                                              |     |

| 28.2.1 BLOCK DIAGRAM                                           | 278 |

| 28.2.2 BLOCK DESCRIPTIONS                                      |     |

| 28.3 REGISTERS                                                 | 278 |

| 28.3.1 REGISTERS SUMMARY                                       |     |

| 28.3.2 DETAIL REGISTER DESCRIPTION                             | 279 |

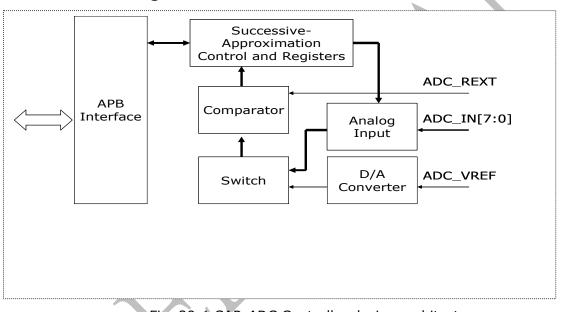

| Chapter 29 SAR-ADC Controller                                  | 281 |

| 29.1 OVERVIEW                                                  | 281 |

| 29.1.1 KEY FEATURES                                            |     |

| 29.2 ARCHITECTURE                                              |     |

| 29.2.1 BLOCK DIAGRAM                                           |     |

| 29.2.2 BLOCK DESCRIPTIONS                                      | 281 |

| 29.3 REGISTERS                                                 | 281 |

| 29.3.1 REGISTERS SUMMARY<br>29.3.2 DETAIL REGISTER DESCRIPTION | 281 |

| 29.3.2 DETAIL REGISTER DESCRIPTION                             |     |

|                                                                |     |

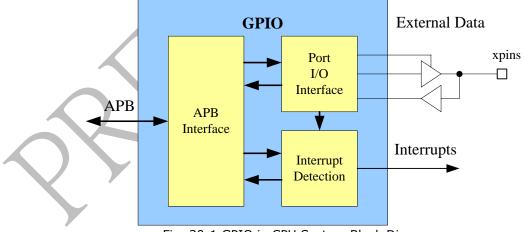

| Chapter 30 GPIO in CPU System                                  |     |

| 30.1 DESIGN OVERVIEW                                           | 283 |

| 30.1.1 OVERVIEW                                                |     |

| 30.1.2 FEATURES                                                | 283 |

| 30.2 ARCHITECTURE                                              | 283 |

| 30.2.1 BLOCK DIAGRAM                                           | 283 |

| 30.2.2 BLOCK DESCRIPTIONS                                      |     |

| 30.3 REGISTERS                                                 | 284 |

| 30.3.1 REGISTERS SUMMARY                                       |     |

| 30.3.2 DETAIL REGISTER DESCRIPTION                             |     |

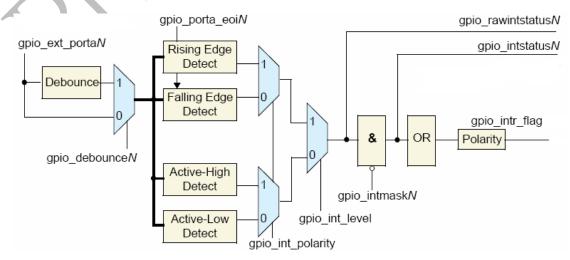

| 30.4 FUNCTIONAL DESCRIPTION                                    |     |

| 30.4.1 OPERATION                                               |     |

|                                                                |     |

| Chapter 31 General Register File in CPU System                 |     |

| 31.1 OVERVIEW                                                  |     |

| 31.2 REGISTERS                                                 |     |

| 31.2.1 REGISTERS SUMMARY                                       |     |

| 31.2.2 DETAIL REGISTERS DESCRIPTION                            |     |

| Chapter 32 Port Multiplexer                                    |     |

| 32.1 OVERVIEW                                                  |     |

| 32.2 DETAILED DESCRIPTION FOR IO MUX                           |     |

| Chapter 33 Hardware Information                                                                                                                                            | 303        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

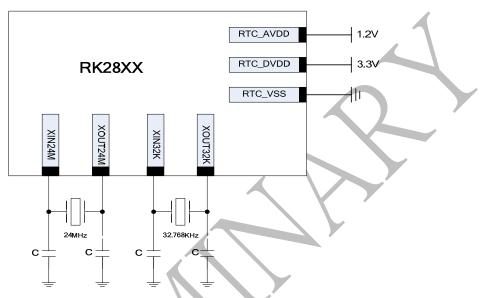

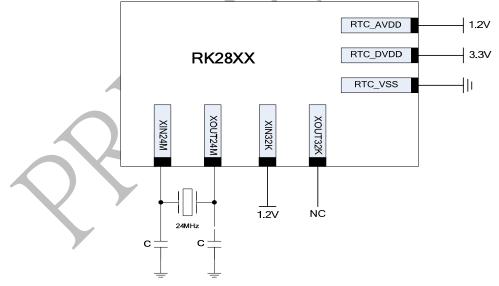

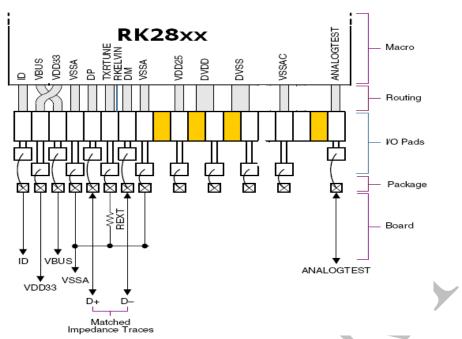

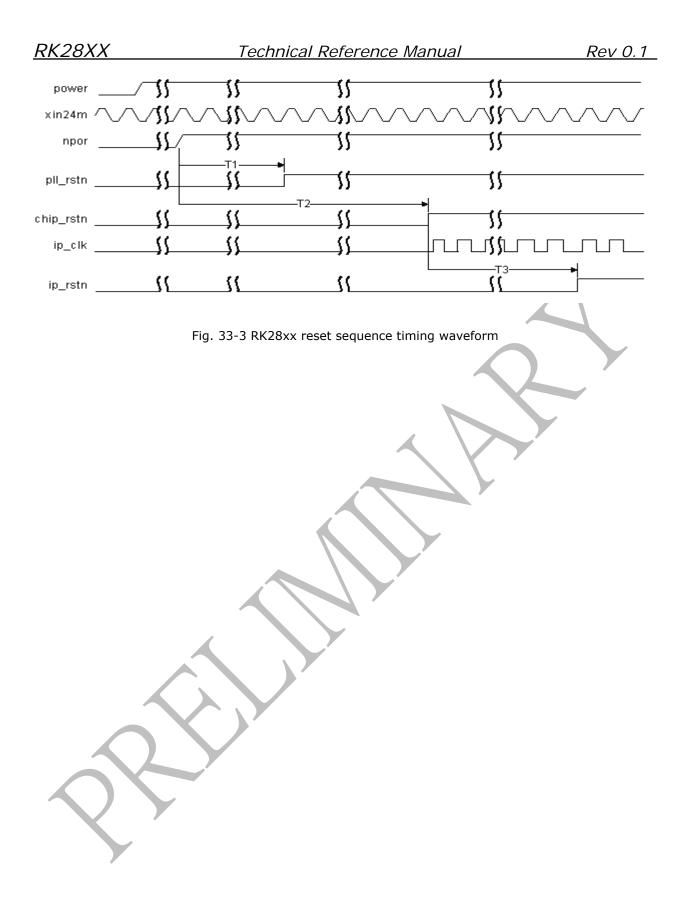

| <ul> <li>33.1 OSCILLATOR CONNECTION</li> <li>33.2 USB PHY CONNECTION</li> <li>33.3 POWER UP SEQUENCE FOR POWER SUPPLY</li> <li>33.4 POWER ON RESET DESCRIPTIONS</li> </ul> | 303<br>304 |

| Chapter 34 Electrical Specification                                                                                                                                        | 306        |

| 34.1 RECOMMENDED OPERATING CONDITIONS                                                                                                                                      |            |

| Appendix A – ARM926EJS16K16K                                                                                                                                               | 307        |

| Appendix B – Refer documents                                                                                                                                               | 308        |

# Figure Index

| 5                                                                          |      |

|----------------------------------------------------------------------------|------|

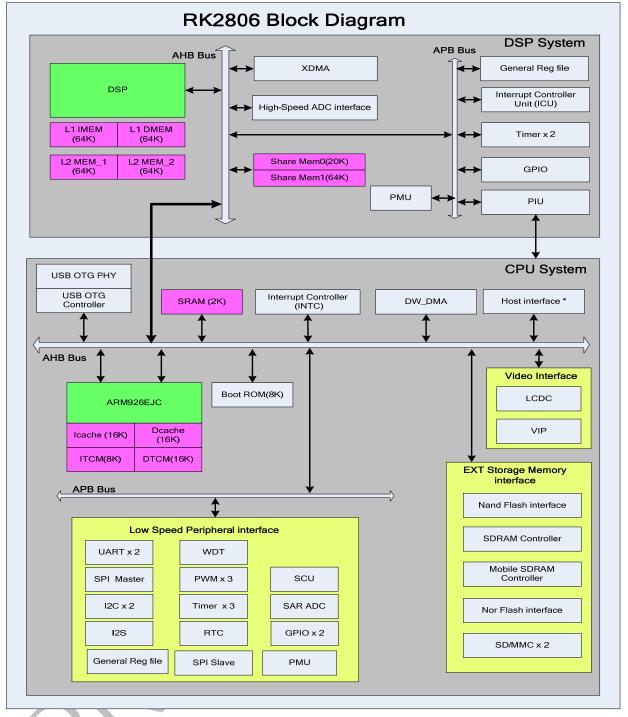

| FIG. 1-1 RK28XX BLOCK DIAGRAM                                              | .20  |

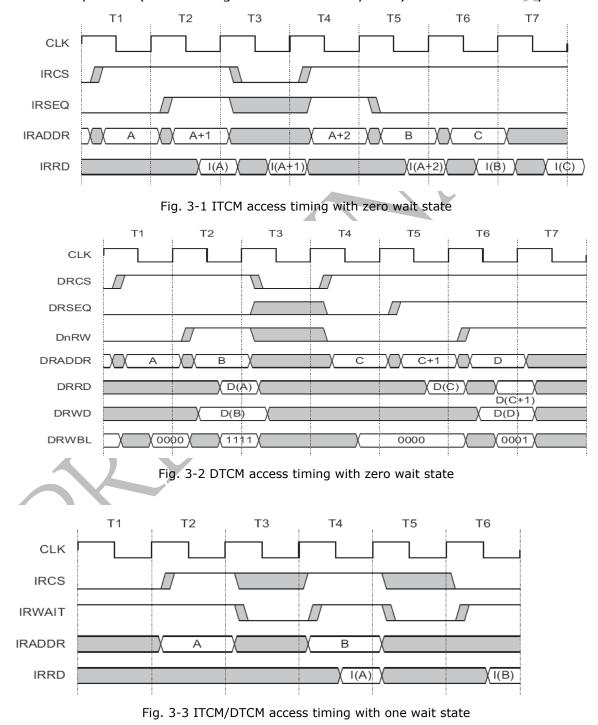

| FIG. 3-1 ITCM ACCESS TIMING WITH ZERO WAIT STATE                           | .31  |

| FIG. 3-2 DTCM ACCESS TIMING WITH ZERO WAIT STATE                           |      |

| FIG. 3-3 ITCM/DTCM ACCESS TIMING WITH ONE WAIT STATE                       |      |

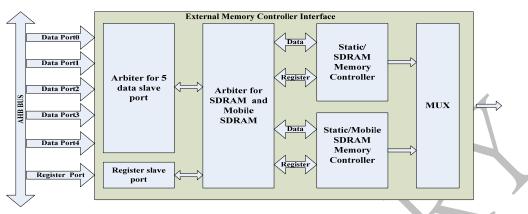

| FIG. 3-4 EXTERNAL MEMORY CONTROLLER ARCHITECTURE                           |      |

|                                                                            |      |

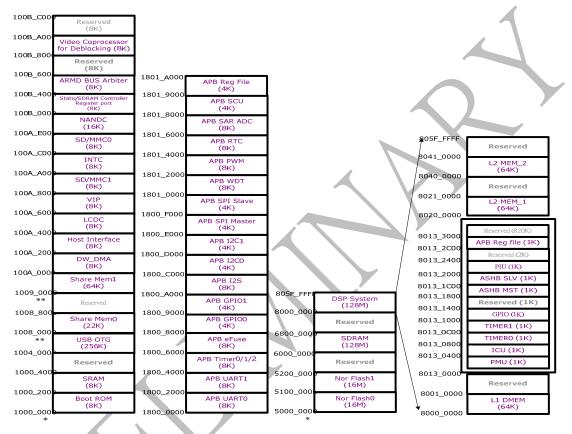

| FIG. 3-5 SYSTEM MEMORY MAP FOR CPU                                         | .33  |

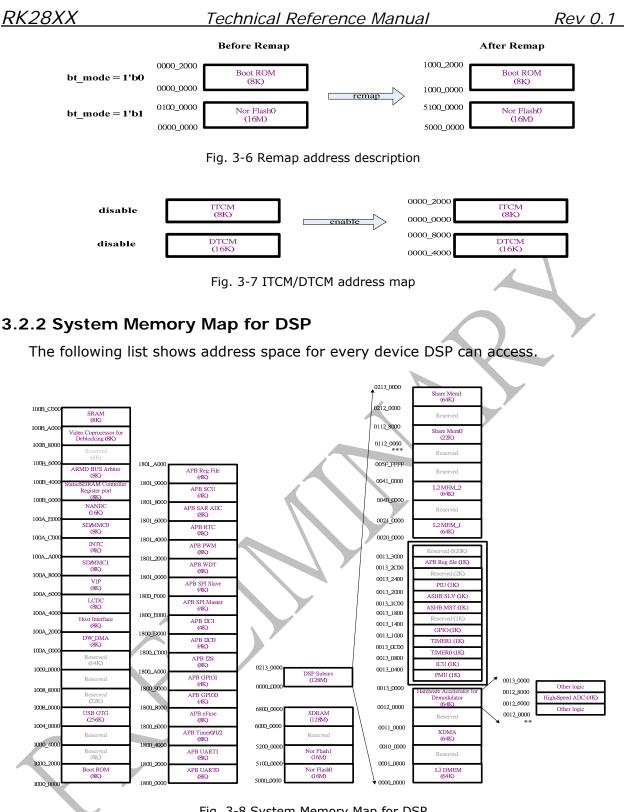

| FIG. 3-6 REMAP ADDRESS DESCRIPTION                                         |      |

| FIG. 3-7 ITCM/DTCM ADDRESS MAP                                             | .34  |

| FIG. 3-8 SYSTEM MEMORY MAP FOR DSP                                         | . 34 |

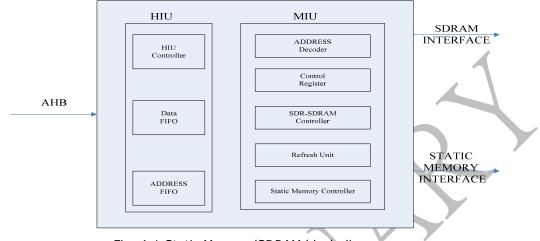

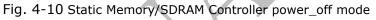

| FIG. 4-1 STATIC MEMORY/SDRAM BLOCK DIAGRAMS                                | .40  |

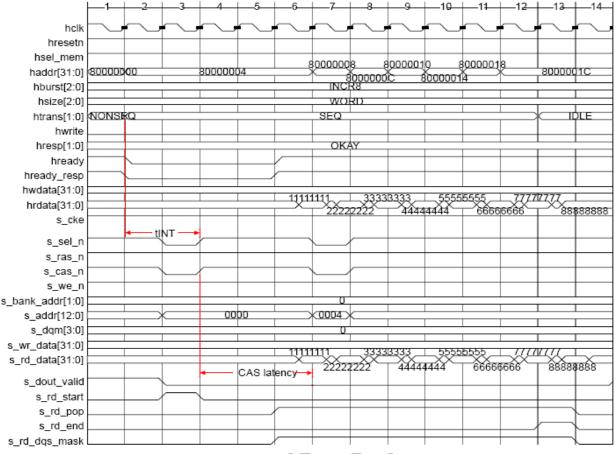

| FIG. 4-2 SDRAM PAGE-HIT SINGLE WRITE                                       | .49  |

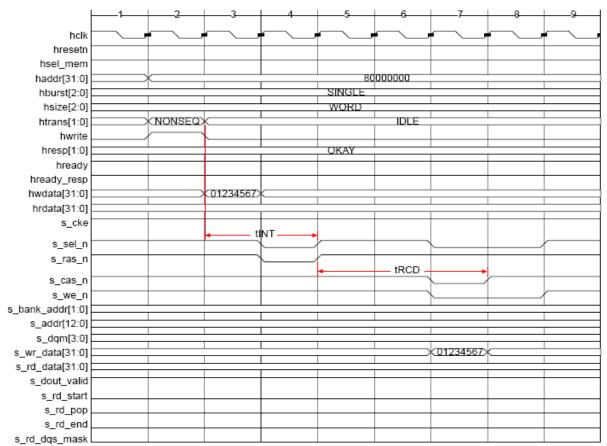

| FIG. 4-3 SDRAM PAGE-MISS SINGLE WRITE                                      | 50   |

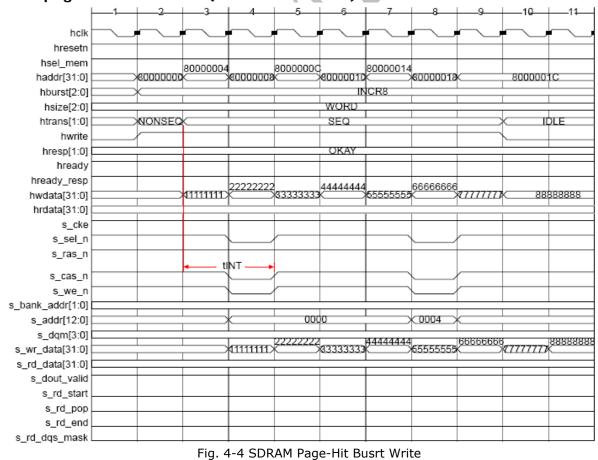

| FIG. 4-4 SDRAM PAGE-HIT BUSRT WRITE                                        | 50   |

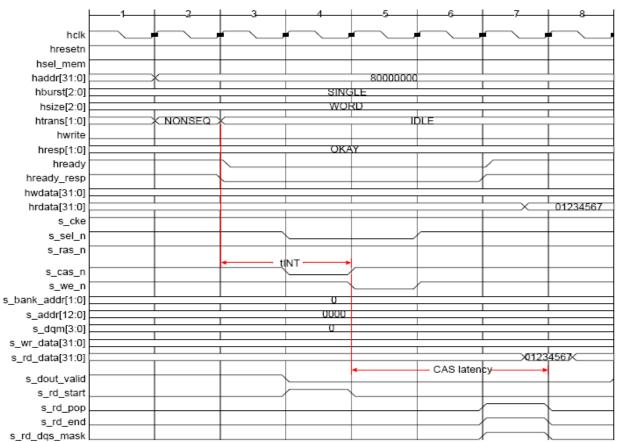

| FIG. 4-5 SDRAM PAGE-HIT SINGLE READ.                                       | 51   |

|                                                                            | .51  |

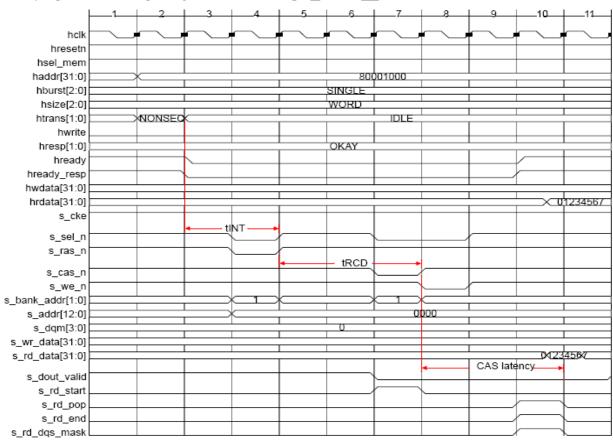

| FIG. 4-6 SDRAM PAGE-MISS SINGLE READ<br>FIG. 4-7 SDRAM PAGE-HIT BUSRT READ | .51  |

|                                                                            | .52  |

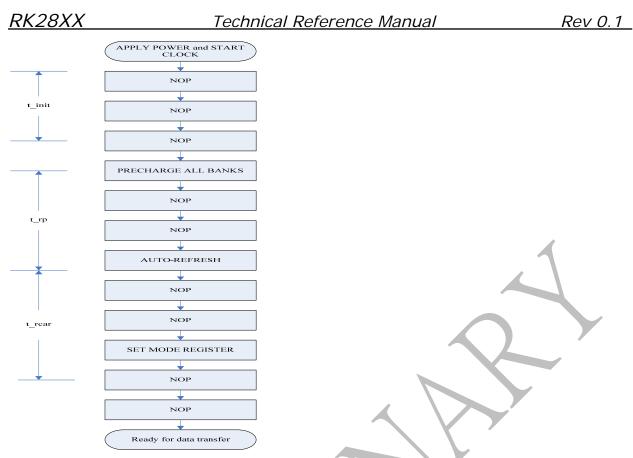

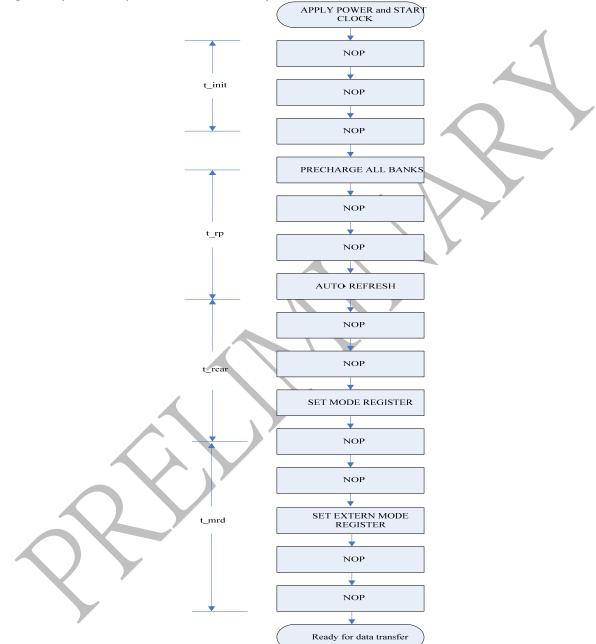

| FIG. 4-8 STATIC MEMORY/SDRAM CONTROLLER POWER ON SEQUENCE                  |      |

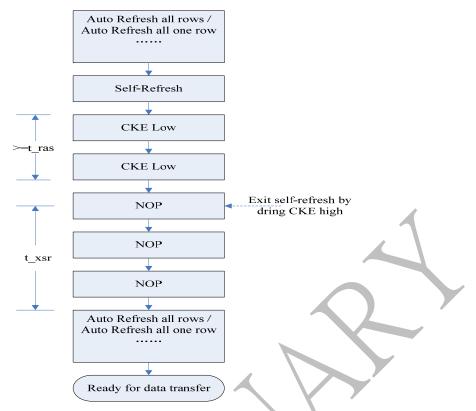

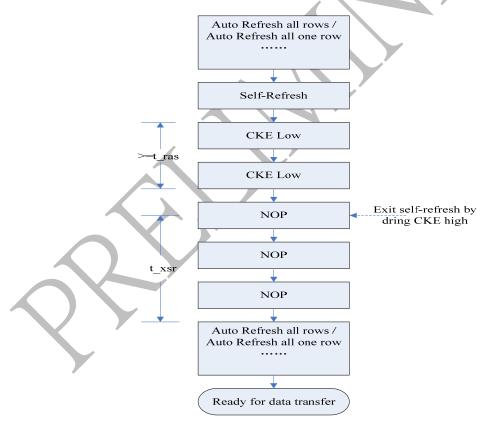

| FIG. 4-9 STATIC MEMORY/SDRAM CONTROLLER SELF_REFLESH MODE                  |      |

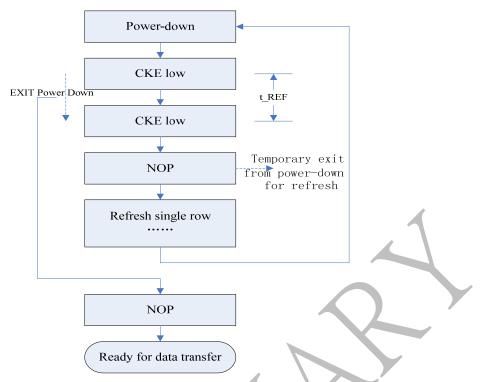

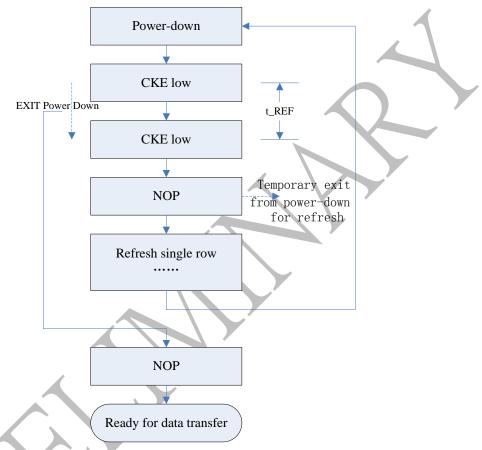

| FIG. 4-10 STATIC MEMORY/SDRAM CONTROLLER POWER_OFF MODE                    |      |

| FIG. 5-1 STATIC MEMORY/MOBILE SDRAM CONTROLLER BLOCK DIAGRAM               |      |

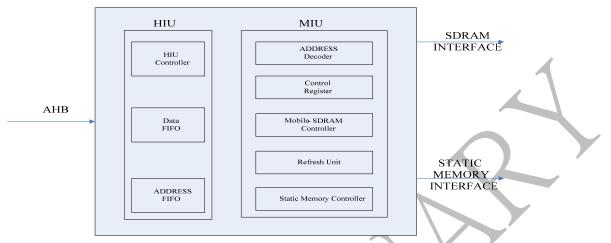

| FIG. 5-2 MOBILE SDRAM PAGE-HIT SINGLE WRITE                                | .68  |

| FIG. 5-3 MOBILE SDRAM PAGE-MISS SINGLE WRITE.                              | .68  |

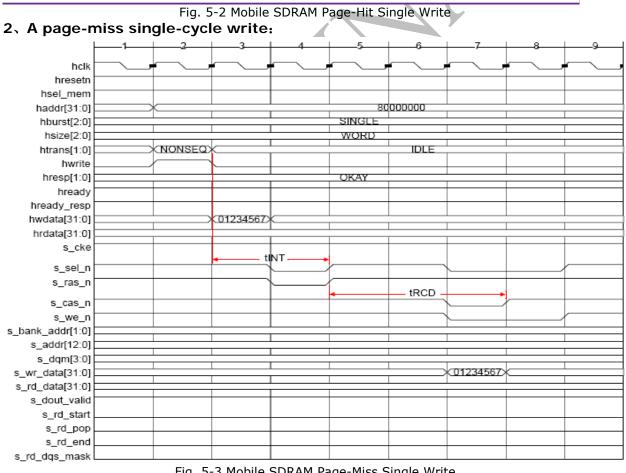

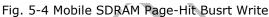

| FIG. 5-4 MOBILE SDRAM PAGE-HIT BUSRT WRITE                                 | 69   |

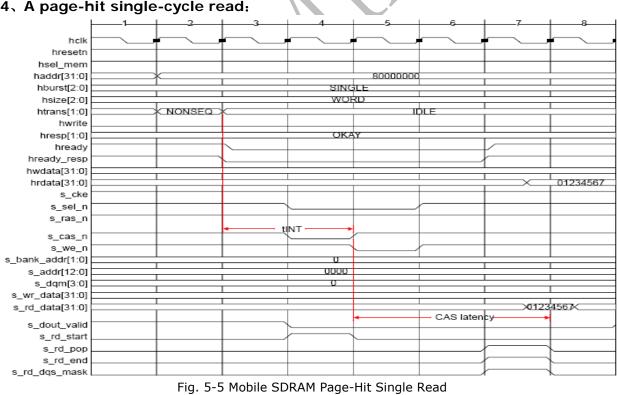

| FIG. 5-5 MOBILE SDRAM PAGE-HIT SINGLE READ                                 | 60   |

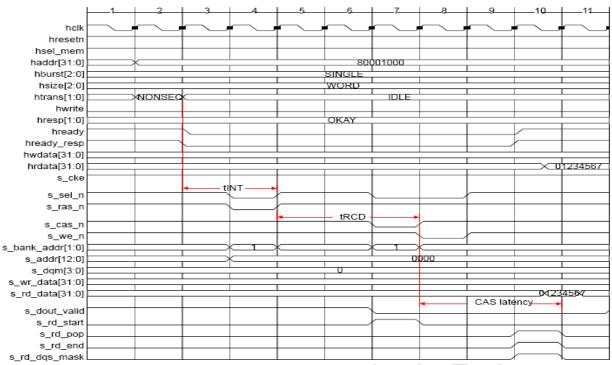

| FIG. 5-6 MOBILE SDRAM PAGE-MISS SINGLE READ                                |      |

|                                                                            |      |

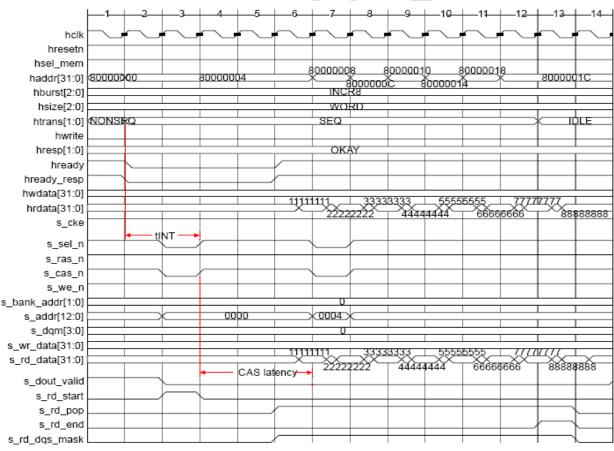

| FIG. 5-7 MOBILE SDRAM PAGE-HIT BUSRT READ                                  | .70  |

| FIG. 5-8 STATIC MEMORY/MOBILE SDRAM CONTROLLER POWER ON SEQUENCE           |      |

| FIG. 5-9 MOBILE SDRAM SELF_REFLESH FLOW                                    |      |

| FIG. 5-10 STATIC MEMORY/MOBILE SDRAM CONTROLLER POWER_OFF MODE             |      |

| FIG. 7-1 SD/MMC HOST CONTROLLER BLOCK DIAGRAM                              |      |

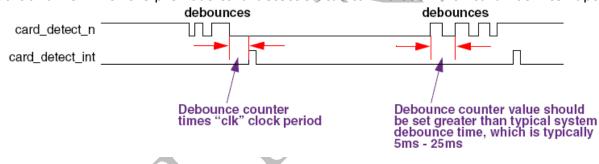

| FIG. 7-2 SD/MMC CARD DETECT TIMING WAVEFORM                                | .80  |

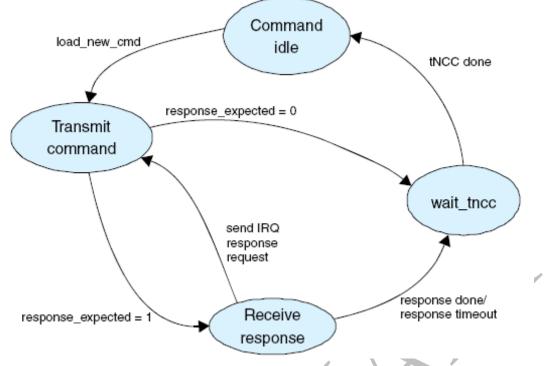

| FIG. 7-3 SD/MMC COMMAND PATH STATE MACHINE                                 | . 82 |

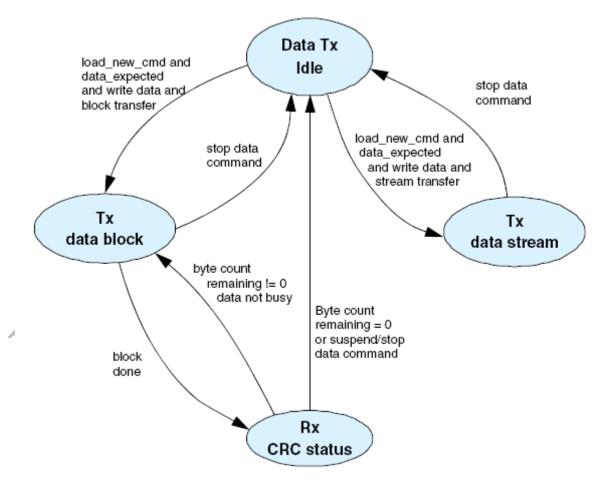

| FIG. 7-4 SD/MMC DATA TRANSMIT STATE MACHINE                                | .83  |

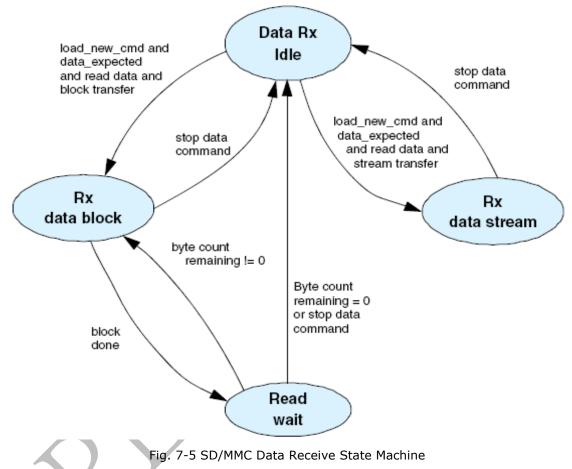

| FIG. 7-5 SD/MMC DATA RECEIVE STATE MACHINE                                 | .85  |

| FIG. 7-6 SD/MMC INITIALIZATION SEQUENCE                                    |      |

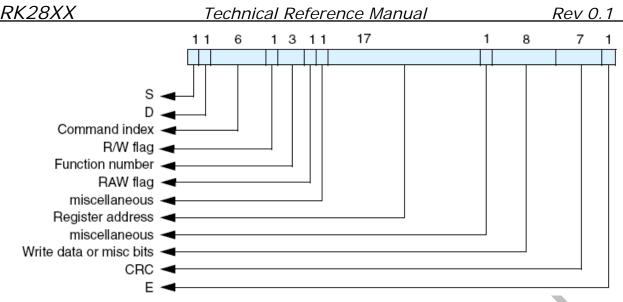

| FIG. 7-7 SD/MMC COMMAND FORMAT FOR CMD52                                   |      |

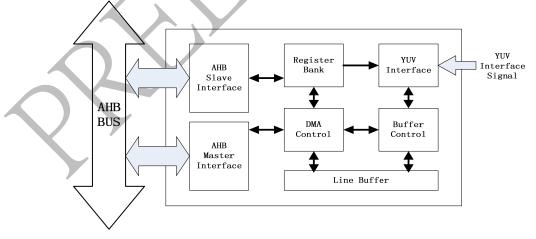

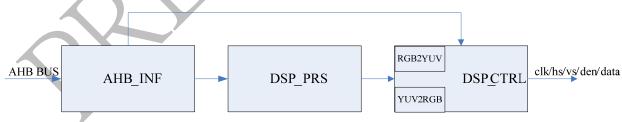

| FIG. 8-1 VIP BLOCK DIAGRAM                                                 |      |

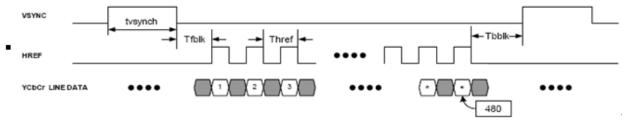

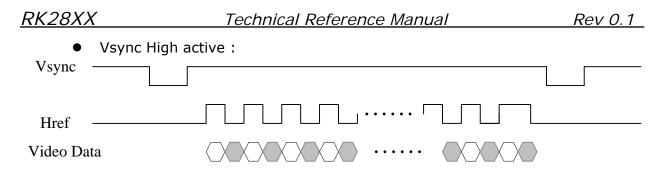

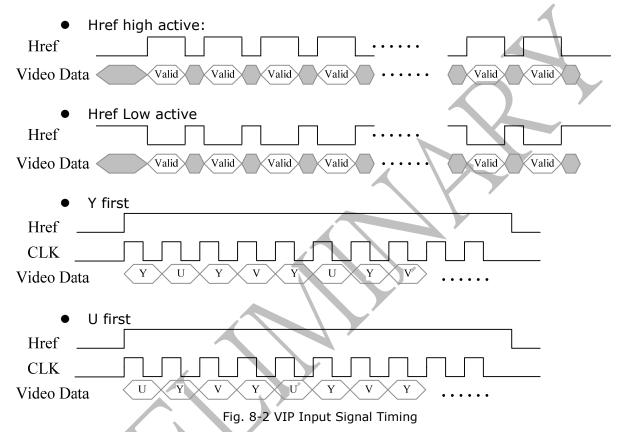

| FIG. 8-2 VIP INPUT SIGNAL TIMING                                           |      |

| FIG. 9-1 LCD CONTROLLER FUNCTION DIAGRAM                                   | 113  |

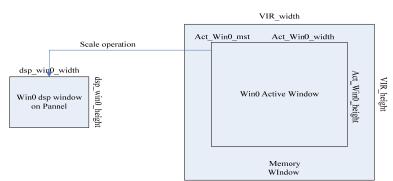

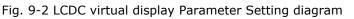

| FIG. 9-2 LCDC VIRTUAL DISPLAY PARAMETER SETTING DIAGRAM                    |      |

|                                                                            |      |

| FIG. 9-3 LCDC WIN1 VIRTUAL DISPLAY PARAMETER SETTING DIAGRAM               |      |

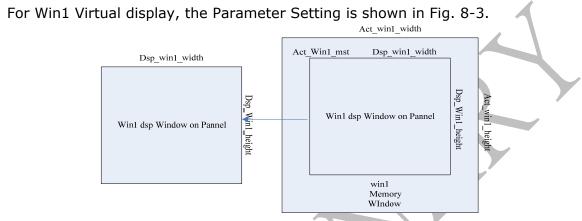

| FIG. 9-4 LCDC WIN0 AND WIN1 DISPLAY ON PANEL DIAGRAM                       |      |

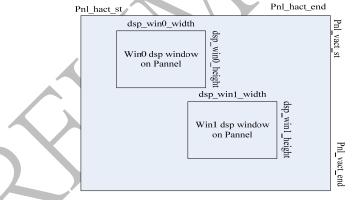

| FIG. 9-5 LCDC HORIZONTAL DISPLAY TIMING WAVEFORM                           |      |

| FIG. 9-6 LCDC VERTICAL PROGRESSIVE DISPLAY TIMING WAVEFORM                 |      |

| FIG. 9-7 LCDC VERTICAL INTERLACE DISPLAY TIMING WAVEFORM                   | 136  |

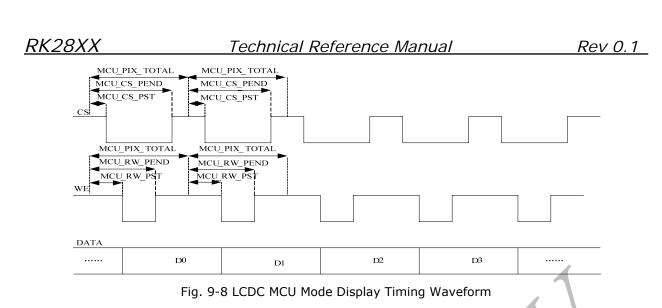

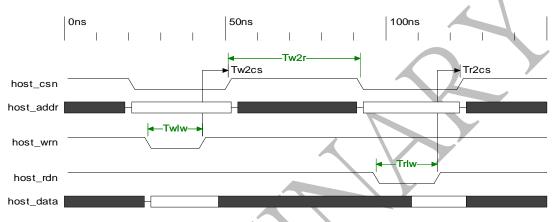

| FIG. 9-8 LCDC MCU MODE DISPLAY TIMING WAVEFORM                             | 137  |

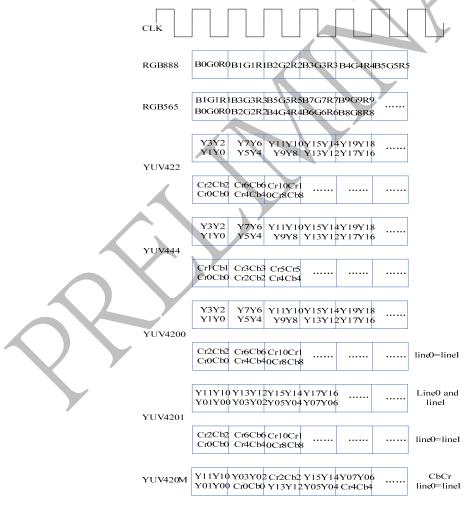

| FIG. 9-9 LCDC INPUT DATA FORMAT DIAGRAM                                    | 137  |

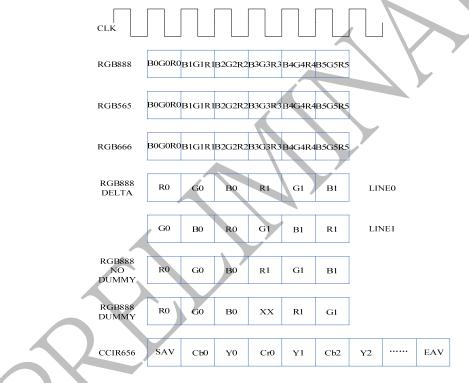

| FIG. 9-10 LCDC OUTPUT DATA FORMAT DIAGRAM                                  |      |

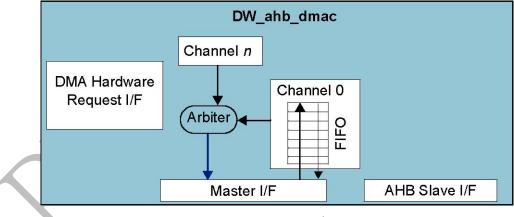

| FIG. 10-1 DW DMA ARCHITECTURE                                              |      |

| FIG. 12-1 INTERRUPT CONTROLLER ARCHITECTURE                                | 162  |

| FIG. 12-2 IRQ INTERRUPT PROCESSING FOR INTC                                |      |

|                                                                            |      |

| FIG. 14-1 HIF BLOCK DIAGRAMS                                               |      |

| FIG. 16-1 RK28XX SYSTEM STOP MODE OPERATION FLOW                           |      |

| FIG. 17-1 RK28XX POWER DOMAIN ARCHITECTURE                                 |      |

| FIG. 18-1 PIU SNOOPING MECHANISM TIMING WAVEFORM                           | -    |

| FIG. 22-1 TIMERS BLOCK DIAGRAM IN CPU SYSTEM                               |      |

| FIG. 22-2 TIMERS USTAGE FLOW IN CPU SYSTEM                                 | 246  |

| FIG. 24-1 WDT BLOCK DIAGRAM                                                | 248  |

| FIG. 24-2 WDT OPERATION FLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 252 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| FIG. 25-1 RTC DESIGN ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .253  |

| FIG. 26-1 I2C CONTROLLER DESIGN ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .254  |

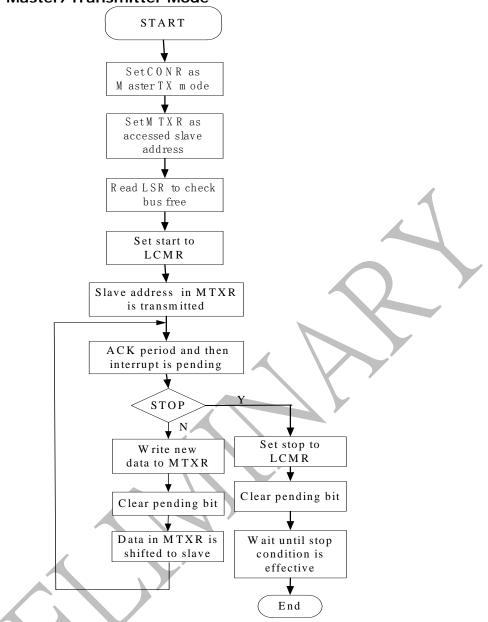

| FIG. 26-2 I2C CONTROLLER OPERATION FLOW IN MASTER/TRANSMITER MODE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .264  |

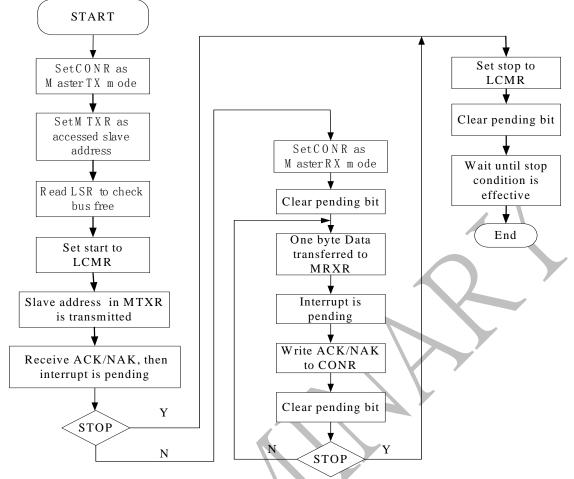

| FIG. 26-3 I2C CONTROLLER OPERATION FLOW IN MASTER/RECEIVER MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .265  |

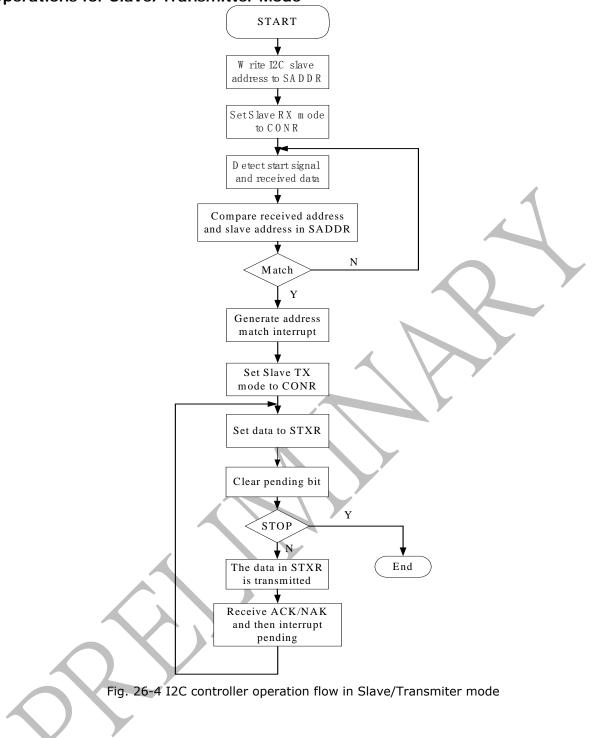

| FIG. 26-4 I2C CONTROLLER OPERATION FLOW IN SLAVE/TRANSMITER MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .266  |

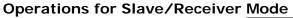

| FIG. 26-5 I2C CONTROLLER OPERATION FLOW IN SLAVE/RECEIVER MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .267  |

| FIG. 27-1 I2S CONTROLLER DESIGN ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

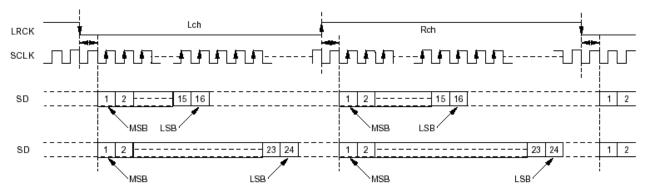

| FIG. 27-2 I2S CONTROLLER TIMING FORMAT FOR I2S INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

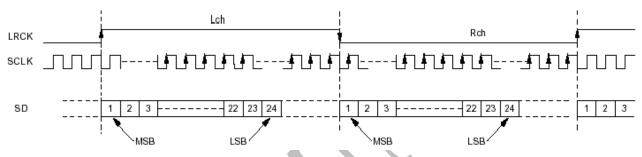

| FIG. 27-3 I2S CONTROLLER TIMING FORMAT FOR LEFT-JUSTIFIED INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

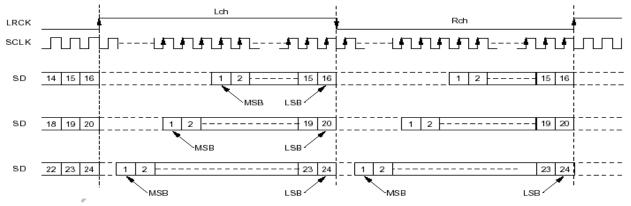

| FIG. 27-4 I2S CONTROLLER TIMING FORMAT FOR RIGHT-JUSTIFIED INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

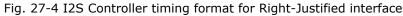

| FIG. 27-5 I2S CONTROLLER TX OPERATION FLOW CHART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 276   |

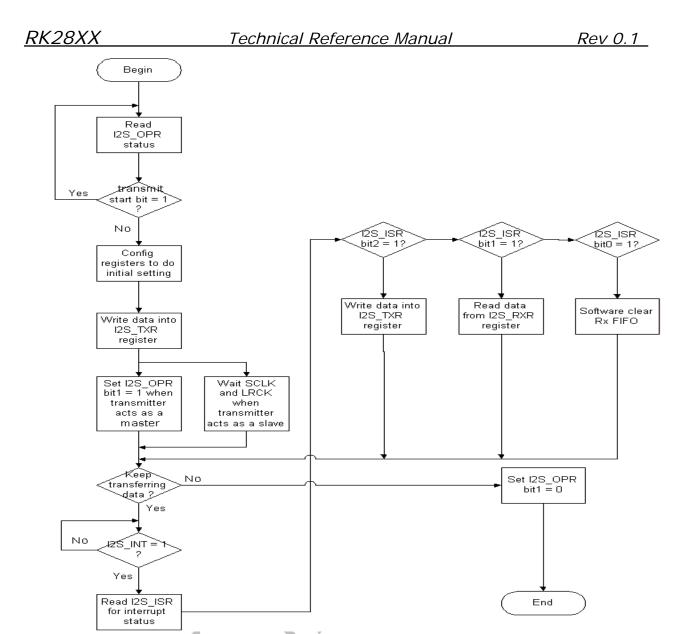

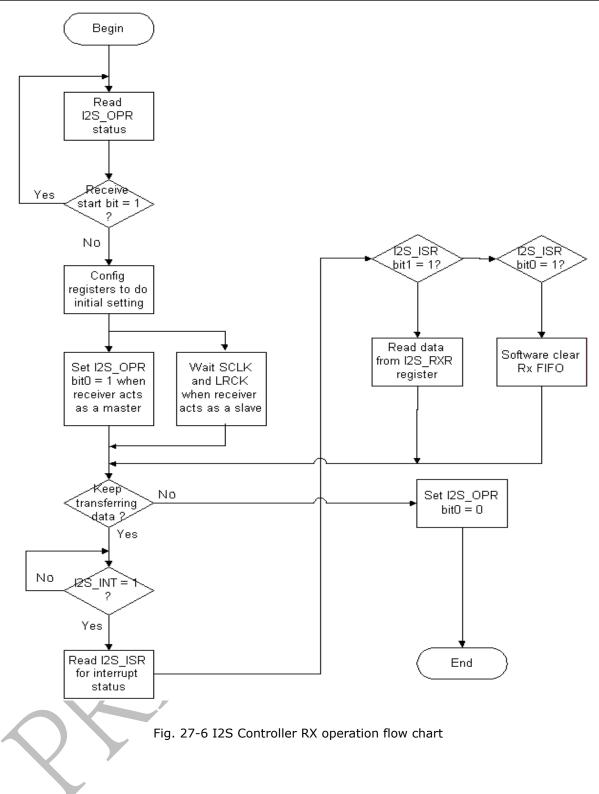

| FIG. 27-6 I2S CONTROLLER RX OPERATION FLOW CHART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| FIG. 28-1 PWM DESIGN ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .278  |

| FIG. 29-1 SAR-ADC CONTROLLER DESIGN ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| FIG. 30-1 GPIO IN CPU SYSTEM BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| FIG. 30-2 GPIO IN CPU SYSTEM INTRRRUPT RTL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 303 |

| FIG. 33-2 RK28XX USB PHY CONNECTION DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| FIG. 33-3 RK28XX RESET SEQUENCE TIMING WAVEFORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 305   |

| The second contracted of the second contract of the second s |       |

# Table Index

| TABLE 3-1 VALID ACCESS PATH LIST FOR CPU AND DSP                                                | 29    |

|-------------------------------------------------------------------------------------------------|-------|

| TABLE 3-2 RK28XX DEBUG MODE DESCRIPTIONS                                                        | 35    |

| TABLE 3-3 RK28XX BOOT MODE DESCRIPTIONS                                                         | 35    |

| TABLE 3-4 INTERRUPT SOURCES CONNECTION FOR CPU                                                  | 35    |

| TABLE 3-5 INTERRUPT SOURCES CONNECTION FOR DSP                                                  | 36    |

| TABLE 3-6 HARDWARE REQUEST CONNECTION FOR DW_DMA                                                | 37    |

| TABLE 3-7 HARDWARE REQUEST CONNECTION FOR XDMA                                                  |       |

| TABLE 7-1 SD/MMC BITS IN INTERRUPT STATUS REGISTER                                              | 77    |

| TABLE 7-2 SD/MMC COMMAND REGISTER SETTINGS FOR NO-DATA COMMAND                                  | ) 103 |

| TABLE 7-3 SD/MMC COMMAND REGISTER SETTING FOR SINGLE-BLOCK OR                                   |       |

| MULTIPLE-BLOCK READ                                                                             | 104   |

| TABLE 7-4 SD/MMC COMMAND REGISTER SETTINGS FOR SINGLE-BLOCK OR                                  |       |

| MULTIPLE-BLOCK WRITE                                                                            | 105   |

| MULTIPLE-BLOCK WRITE<br>TABLE 7-5 SD/MMC PARAMETERS FOR CMDARG REGISTERS                        | 107   |

| TABLE 7-6 SD/MMC CMDARG BIT VALUES         TABLE 7-7 SD/MMC AUTO-STOP GENERATION CONDITION LIST | 108   |

| TABLE 7-7 SD/MMC AUTO-STOP GENERATION CONDITION LIST                                            | 111   |

| TABLE 9-1 LCDC PIN MAPPING WITH PANNEL TYPE                                                     | 书签。   |

| TABLE 10-1 DW DMA CTLX.SRC MSIZE AND DEST MSIZE DECODING                                        | 148   |

| TABLE 10-2 DW_DMA CTLX.SRC_TR_WIDTH AND CTLX.DST_TR_WIDTH DECOL                                 | DING  |

|                                                                                                 | 148   |

| TABLE 10-3 DW DMA CTLX TT EC FIELD DECODING                                                     | 148   |

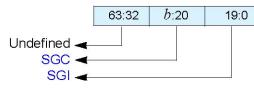

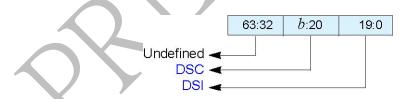

| TABLE 10-4 DW_DMA PROTCTL FIELD TO HPROT MAPPING                                                | 152   |

| TABLE 10-5 DW_DMA DESTINATION SCATTER REGISTER DESCRIPTION FOR                                  |       |

| CHANNEL X                                                                                       | 153   |

| TABLE 10-6 PROGRAMMING OF TRANSFER TYPES AND CHANNEL REGISTER                                   |       |

| UPDATE METHOD                                                                                   | 159   |

| TABLE 14-1 PIN MAPPING BETWEEN HIF AND LCDC INTERFACE                                           |       |

| TABLE 32-1 RK28XX IO MUX LIST                                                                   | 298   |

|                                                                                                 |       |

# Acronym descriptions

| CXCLK | clock for DSP Core                  |

|-------|-------------------------------------|

| XHCLK | clock for AHB bus inside DSP System |

| XPCLK | clock for APB bus inside DSP System |

| R     | Read only                           |

| RW    | Capable of both read and write      |

| R/W   | Capable of both read and write      |

# Chapter 1 Introduction

### 1.1 Overview

RK28xx is a highly-integrated, high-performance, low-power digital multimedia processor which is based on Dual Core (DSP+CPU) architecture with hardware accelerator. It is designed for high-end multimedia product applications such as PMP, GPS and Mobile TV etc.

RK28xx can support decode and encode for various types of video standards such as H.264/RMVB/MPEG-4/AVS/WMV9 by software and dedicated coprocessors. Specially, highest performace for video decode will reach fluent replay for video with H.264 @ 1280x720 formats. Meanwhile, RK28xx can also support many types of mobile TV standards by software and dedicated hardware accelerators, such as DVB-T, CMMB, T-DMB etc. By providing a complete set of peripheral interface, RK28xx can support very flexible applications , including SDRAM, Nor Flash, Nand Flash, LCDC , Sensor, USB OTG , SD/MMC , Wi-Fi , High-speed ADC , I2C, I2S , UART , SPI , PWM etc.

This document will provide guideline on how to use RK28xx correctly and efficiently. In them, the chapter 1 and chapter 2 will introduce the features, block diagram, and signal descriptions and system configuration of RK28xx, the chapter 3 through chapter 37 will describe the full function of each module in detail.

### 1.2 Features

- System Operation

- Dual Core Architecture (ARM926EJC + DSP), including hardware accelerator

- Support system boot sequentially from ARM to DSP

- Support address remap function

- For two cores, all modules have unified address space

- Selectable JTAG debug method

- ARM9 debug only (default)

- DSP debug only

- ◆ ARM9+DSP dual core debug

- Selectable booting method

- Boot from NOR Flash

- Boot from Embedded ROM (default)

- Memory Organization

- Internal memory space for ARM processor

- ◆ Internal 16KB SRAM for ARM9 ICache

- Internal 16KB SRAM for ARM9 DCache

- ◆ Internal 8KB SRAM for ARM9 ITCM

- ◆ Internal 16KB SRAM for ARM9 DTCM

- Internal memory space for DSP processor

- Internal 64KB SRAM for DSP Instruction L1 Memory (Also config as 32KB Memory+32KB ICache by software)

- Internal 64KB SRAM for DSP Data L1 Memory

- Internal 64KB SRAM for DSP Instruction L2 Memory

- ◆ Internal 64KB SRAM for DSP Data L2 Memory

- Embedded 8KB ROM for ARM9 Boot

- Embedded 2KB SRAM for communication between two cores

- Embedded 90KB SRAM for share among ARM,DSP

- Communication between two cores

- Support share memory and interactive interrupt method to complete communication

- Processor Interface Unit (PIU)

- Built-in three Command/reply protocols registers and three Semaphore registers to accessed by two cores

- Support three semaphore-related interrupts and one command-reply-related interrupt between two cores

- Clock & Power Management

- Three on-chip PLLs for ARM9 subsystem, DSP subsystem and Other logic

- Support different DSP Core and internal AHB Bus clock ratio : 1:1, 1:2, 1:3, 1:4, up to 1:16 mode

- Support different DSP internal AHB Bus and internal APB Bus clock ratio: 1:1, 1:2, 1:3, 1:4, up to 1:16 mode

- Support different ARM9 core and AHB Bus clock ratio: 1:1, 1:2, 1:3 and 1:4 mode

- Support different ARM AHB Bus and ARM APB Bus clock ratio: 1:1, 1:2 and 1:4 mode

- Max frequency of every key clock domain

- ♦ 400MHz Max frequency for DSP Core

- 350MHz Max frequency for ARM Core

- 6 types of work modes by clock gating to save power :

- Normal mode : Normal operating mode

- Slow mode : Low frequency clock (24MHz) without PLL

- Deep Slow mode : More Low frequency clock (32.768KHz) without PLL

- ◆ Idle mode : The clock for only CPU is stopped ,

- Wake up by any interrupts to CPU from idle mode

- Sleep mode

The clock for only DSP is stopped , Wake up from sleep mode by some interrupts to DSP or register set from CPU

- Stop mode

All clocks will be stopped , and SDRAM into Self-refresh, all PLLs into power-down mode, Wake up from stop mode by external pin or RTC alarm

- interrupt

- Support power supply shut down for 4 domain separately

### • Memory Interface

- Static/SDRAM Memory controller

- Dynamic memory interface support , including SDR-SDRAM and Mobile SDRAM

- Asynchronous static memory device support including SRAM, ROM and Nor Flash with or without asynchronous page mode

- Support 1 chip selects for (Mobile) SDRAM and 2 chip selects for static memory

- Support 32bits data bus (Mobile) SDRAM and 8/16 bits data bus static memory

- Support industrial standard (Mobile) SDRAM from 16MB to 128 MB devices

- 4Mbytes access space per static memory support

- Support (Mobile) SDRAM and Static Memory power-down mode

- Support (Mobile) SDRAM self-refresh mode

- Programmable arbitration priority for 5 slave data ports

- Nand Flash controller

- Support 4 chip selects for nand flash

- support 8bits wide data

- Flexible CPU interface support

- Embedded 4x512B size buffer to improve performace

- Support internal DMA transfer from/to flash

- ♦ 512B、2KB、4KB page size support

- Support hardware ECC

- SD/MMC controller

- Two Embedded SD/MMC Controllers, one is 4bit data bus , another is 8bit data bus

- Compliant with SD Memory/SDIO with 1bit and 4bit data bus

- Compliant with MMC V3.3 and V4.0 with 1/4/8bit data bus

- Support combined single 32x32bits FIFO for both transmit and receive operations

- Support FIFO over-run and under-run prevention by stopping card clock

- Variable SD/MMC card clock rate 0 52 MHz which depends on AHB clock frequency

- Controllable SD/MMC card clock to save power consumption

- Support card detection and initialization , and write protection

- Support transfer block size of 1 to 65365Bytes

- DMA based or Interrupt based operation

### • VIDEO interface

- Sensor controller

- Support 24MHz, 48MHz, 27MHz clock input

- Support CCIR656 PAL/NTSC

- Support YUYV and UYVY format input

- Support YUV 4:2:2 and YUV 4:2:0 format output

- Programmable Hsync and Vsync porality

- Support 8 MegaPixels

- LCD controller

- Embedded DMA function

- Support one SCALE window and one no SCALE window

- YUV422/YUV420/RGB565/RGB888 Input are Supported in SCALE window

- RGB565/RGB888 Input and 4 AREAS are Supported in NO SCALE window

- Support Virtual Display

- Build in scaler engine from 1/8 to 8

- Support 16 grade alpha blending and transparent operation.

- Support Blank/Black Function

- Support LCD Pannel resolution up to 1280x760

- Compatible with MCU Pannel

- Support MCU PANNEL Bypass Mode and SCALE Mode

- Compatible with RGB Delta/no-Delta Pannel

- Compatible with RGB Series/Parallel 24bits (max) Output

- Compatible with CCIR656 output

- Support Interlace and Progressive Output

- Support LCDC high-z control

- Support LCDC interface bypass from Host interface

### • DMA Controller

- Two DMA Controllers in chip

- DW\_DMA Controller integrated inside ARM9 subsystem

- Three DMA Channels support to use by audio , sd/mmc and system data transfer

- 8 hardware request handshaking support

- Support hardware and software trigger DMA transfer mode

- Build-in 3 data FIFO : 64Bytes/32Bytes/16Bytes

- Scatter/Gather transfer support

- LLP transfer support

- Two masters for on-the-fly support

- The master interface only support undefined length INCR transfer

- 3D-DMA Controller(XDMA) integrated inside DSP subsystem

- This DMA focus on data transfer for video process and mobile TV

application

- 16 configurable DMA channels, 4 channels support 3-dimensional data transfer

- 8/16/32/64bit data transfer support and configurable burst length (INCR/INCR4/INCR8)

- Programmable source and destination addresses with a post-modification option

- Configurable external channel triggering (edge or level)

- Support chaining-channels ,linked list-transfer and auto-channel initialization operating mode

- Pause and resume operations supported to save power

- Eight-stage memory buffer FIFO

### • Interrupt Controller

- Two Interrupt Controller in chip

- DW\_INTC integrated inside ARM9 subsystem

- Support 32 IRQ normal interrupt sources and 4 FIQ fast interrupt sources

- Vectored interrupts support

- Software interrupts support

- Programmable interrupt priorities

- Programmable High/Low Level sensitive or Negative / Positive edge triggered interrupts

- ICU (Interrupt Control unit) integrated inside DSP subsystem

- 48 interrupt sources , each may be linked to different interrupt inputs for DSP core

- Software triggering to all 48 interrupt sources

- Configurable source interrupt polarity (low/high)

- External interrupt source with software configuration to edge/level sensitive

### • USB interface

- Complies with the OTG Supplement to the USB2.0 Specification

- Operates in High-Speed and Full-Speed mode

- Support Session Request Protocol(SRP) and Host Negotiation Protocol(HNP)

- Support 6 channels in host mode

- 6 endpoints , 3 in and 3 out

- Built-in one 1777 x 35bits FIFO

- HOST interface

- 16 bits data bus for data transfer

- 2KB internal Dual Port SRAM buffer

- Interrupt request for data exchange

- Support Host interface function disable

- Support address self-increment when accessing buffer by MCU interface

### • Low\_speed Peripheral interface

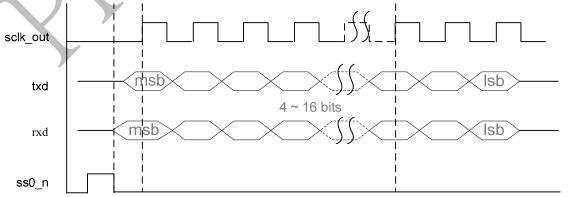

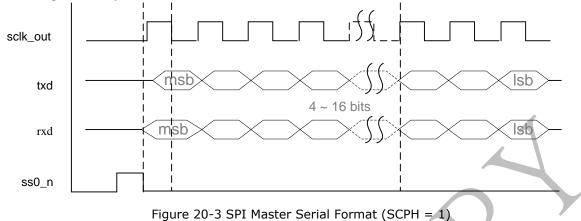

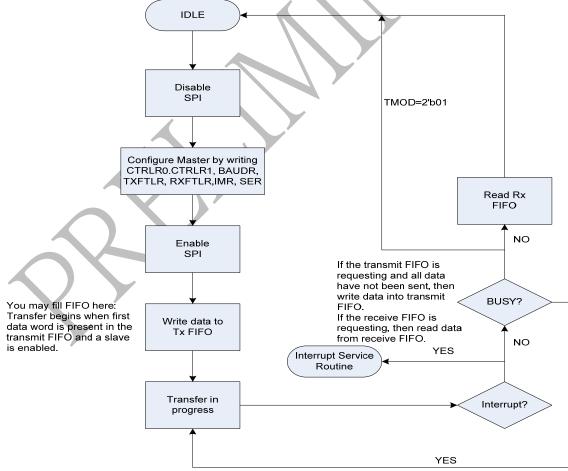

- Serial Peripheral Interface (SPI) Master Controller

- Support two slave devices connection

- Compatible with Motorola SPI , TI Synchronous Serial Protocol or National Semiconductor Microwire interface

- Dynamic control of serial bit rate of data transfer by programmable sclk\_out frequency, which is half of PCLK in max mode

- FIFO depth for transmit and receive are also 16x16bits

- Programmable data item size ,from 4 to 16bits

- DMA based and interrupt based operation

- Serial Peripheral Interface (SPI) Slave Controller

- Compatible with Motorola SPI, TI Synchronous Serial Protocol or National Semiconductor Microwire interface

- Dynamic control of serial bit rate of data transfer by sclk\_in from master device

- FIFO depth for transmit and receive are also 16x16bits

- Programmable data item size ,from 4 to 16bits

- DMA based and interrupt based operation

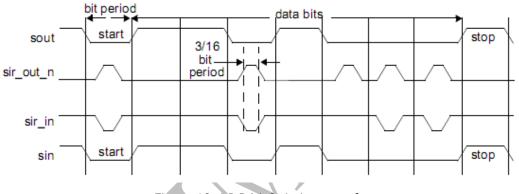

- UARTO

- Based on the 16550 industry standard

- UARTO support modem function and Serial data transfer

- Programmable serial data baud rate , up to 1.5Mbps

- DMA based and interrupt based operation

- FIFO depth for data transfer is 32x8bits

- UART1

- Based on the 16550 industry standard

- UART1 support IrDA 1.0 SIR mode and Serial data transfer

- Programmable serial data baud rate , up to 1.5Mbps .

- In IrDA SIR mode, support configurable baud data rate up to 115.2K and a pulse duration as specified in the IrDA physical layer specification

- DMA based and interrupt based operation

- FIFO depth for data transfer is 32x8bits

- I2C controller

- ♦ 2 I2C controllers integrated in chip

- Multi masters operation support

- Software programmable clock frequency and transfer rate up to 100Kbit/s in standard mode or up to 400Kbit/s in Fast mode

- Supports 7 bits and 10 bits addressing modes

- I2S

- Support mono/stereo audio file

- Support audio resolution: 8, 16 bits

- Support audio sample rate from 32KHz to 96 KHz

- Support I2S, Left-Justified and Right-Justified digital serial data format

- PWM

- Built-in three 32 bit timer modulers

- Programmable counter

- Chained timer for long period purpose

- 4-channel 32-bit timer with Pulse Width Modulation (PWM)

- Programmable duty-cycle, and frequency output

- General Purpose IO (GPIO)

- Support 96 individually programmable input/output pins

- ◆ 16 GPIOs with external interrupt capability

- Timers in CPU system

- Built-in Three 32 bits timer modules

- Support for two operation modes : free-running and user-defined count

- Timers in DSP system

- Built-in two 32 bits timer modules

- Support for 5 various counting modes : Single Count mode, Auto-restart mode , Free-running , Event Count mode and Watchdog Timer mode

- Pulse Width Modulation(PWM) mechanism

- $\blacklozenge$  Three possible input clock signals: internal , external and cascaded

- Watchdog Timer (WDT)

- Watchdog function (Generate a system reset or an interrupt)

- Built-in 32 bits programmable counter

- Real Time Clock (RTC)

- Support perpetual RTC core power

- Programmable alarm with interrupt for system power wake up

- System power off sequence with output control pin

- RTC core power loss indication

- Analog IP interface

- ADC Converter

- 4-channel single-ended 10-bit 1MSPS Successive Approximation Register (SAR) analog-to-digital converter

- No off-chip components required

- DNL less than +/-1 LSB , INL less than +/-1.5 LSB

- Supply 2.8V to 3.6V for analog interface

- eFuse

- ◆ 64-bit serial eFuse macro

- Be programmed one bit at a time, but all 64bits can be read at the same time.

- 2.9V (+/-200mV) & 2.5V(+/-50mV) Programm voltage

- Operation Temperature Range

TBD

- Operation Voltage Range

- Core: 1.2V

- I/O: 3.3V/2.5V/1.8V (2.5V for USB OTG PHY, 1.8V for Mobile SDRAM)

- Package Type

- RK2806 BGA256 (14mmX14mm body size), for PMP application

- Other package type TBD

- Power

- TBD

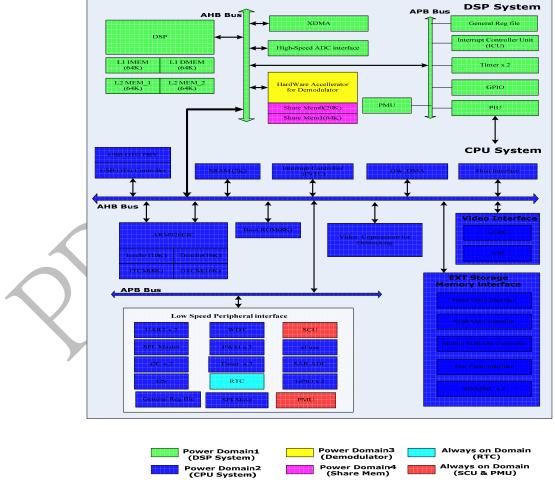

### 1.3 Block Diagram

The following figure shows block diagram of RK28xx.

RK28xx can be divided into two sub system : DSP System and CPU System.

- DSP System

- XDMA : three-dimensional DMA , used to data transfer for video decoder or other algorithm

- High-Speed ADC Interface : focus on completing data reveiver from tuner in DVB-T,DAB, T-DMB,GPS application with software method.

- ICU : Interrupt controller for DSP processor

- PIU : processor interface unit, used to complete communication between DSP and CPU